Difference between revisions of "STM32F103 Microcontroller"

(→Pinout) |

(→Flash uploader) |

||

| (8 intermediate revisions by 2 users not shown) | |||

| Line 3: | Line 3: | ||

Key features of the STM32F103RET6 microcontroller | Key features of the STM32F103RET6 microcontroller | ||

| + | |||

| + | ==Overview== | ||

| + | *Core: ARM 32-bit CortexTM-M3 CPU | ||

| + | ** 72 MHz maximum frequency, 1.25 DMIPS/MHz (Dhrystone 2.1) performance at 0 wait state memory access | ||

| + | ** Single-cycle multiplication and hardware division | ||

| + | * Memories | ||

| + | ** 256 to 512 Kbytes of Flash memory | ||

| + | ** up to 64 Kbytes of SRAM | ||

| + | ** Flexible static memory controller with 4 Chip Select. Supports Compact Flash, SRAM, PSRAM, NOR and NAND memories | ||

| + | ** LCD parallel interface, 8080/6800 modes | ||

| + | * Clock, reset and supply management | ||

| + | ** 2.0 to 3.6 V application supply and I/Os | ||

| + | ** POR, PDR, and programmable voltage detector (PVD) | ||

| + | ** 4-to-16 MHz crystal oscillator | ||

| + | ** Internal 8 MHz factory-trimmed RC | ||

| + | ** Internal 40 kHz RC with calibration | ||

| + | ** 32 kHz oscillator for RTC with calibration | ||

| + | * Low power | ||

| + | ** Sleep, Stop and Standby modes | ||

| + | ** VBAT supply for RTC and backup registers | ||

| + | * 3 × 12-bit, 1 μs A/D converters (up to 21 channels) | ||

| + | ** Conversion range: 0 to 3.6 V | ||

| + | ** Triple-sample and hold capability | ||

| + | ** Temperature sensor | ||

| + | * 2 × 12-bit D/A converters | ||

| + | * DMA: 12-channel DMA controller | ||

| + | ** Supported peripherals: timers, ADCs, DAC, SDIO, I2Ss, SPIs, I2Cs and USARTs | ||

| + | * Debug mode | ||

| + | ** Serial wire debug (SWD) & JTAG interfaces | ||

| + | ** Cortex-M3 Embedded Trace MacrocellTM | ||

| + | * Up to 112 fast I/O ports | ||

| + | ** 51/80/112 I/Os, all mappable on 16 external interrupt vectors and almost all 5 V-tolerant | ||

| + | * Up to 11 timers | ||

| + | ** Up to four 16-bit timers, each with up to 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input | ||

| + | ** 2 × 16-bit motor control PWM timers with dead-time generation and emergency stop | ||

| + | ** 2 × watchdog timers (Independent and Window) | ||

| + | ** SysTick timer: a 24-bit downcounter | ||

| + | ** 2 × 16-bit basic timers to drive the DAC | ||

| + | * Up to 13 communication interfaces | ||

| + | ** Up to 2 × I2C interfaces (SMBus/PMBus) | ||

| + | ** Up to 5 USARTs (ISO 7816 interface, LIN, IrDA capability, modem control) | ||

| + | ** Up to 3 SPIs (18 Mbit/s), 2 with I2S interface multiplexed | ||

| + | ** CAN interface (2.0B Active) | ||

| + | ** USB 2.0 full speed interface | ||

| + | ** SDIO interface | ||

| + | * CRC calculation unit, 96-bit unique ID | ||

| + | * ECOP ACK® packages | ||

== Documents and files == | == Documents and files == | ||

| Line 130: | Line 177: | ||

== Flash uploader == | == Flash uploader == | ||

Command line parameters for STMFlashLoader.exe: | Command line parameters for STMFlashLoader.exe: | ||

| − | -c --pn 3 --br 115200 --db 8 --sb 1 --to 1000 -i "STM32_High-density_512K" -e --all -d --fn "#H" | + | -c --pn 3 --br 115200 --db 8 --sb 1 --to 1000 -i "STM32_High-density_512K" -e --all -d --fn "#H" |

--pn 3 indicates com port: COM3 | --pn 3 indicates com port: COM3 | ||

| Line 143: | Line 190: | ||

*All pins without a special function can be used as general purpose digital Input or Output (GPIO) | *All pins without a special function can be used as general purpose digital Input or Output (GPIO) | ||

*Warning: do not set special function pins in output mode without consulting the stamp schematic | *Warning: do not set special function pins in output mode without consulting the stamp schematic | ||

| + | *Pins are 5V tolerant | ||

{| class="wikitable" border="1" cellspacing="0" | {| class="wikitable" border="1" cellspacing="0" | ||

| Line 151: | Line 199: | ||

! Function 3 | ! Function 3 | ||

! Function 4 | ! Function 4 | ||

| − | |||

|- | |- | ||

| PA0 | | PA0 | ||

| Line 158: | Line 205: | ||

| ADC0 | | ADC0 | ||

| TIM2_CH1_ETR | | TIM2_CH1_ETR | ||

| − | |||

|- | |- | ||

| PA1 | | PA1 | ||

| Line 165: | Line 211: | ||

| TIM2_CH2 | | TIM2_CH2 | ||

| | | | ||

| − | |||

|- | |- | ||

| PA2 | | PA2 | ||

| Line 172: | Line 217: | ||

| TIM2_CH3 | | TIM2_CH3 | ||

| | | | ||

| − | |||

|- | |- | ||

| PA3 | | PA3 | ||

| Line 179: | Line 223: | ||

| TIM2_CH4 | | TIM2_CH4 | ||

| | | | ||

| − | |||

|- | |- | ||

| PA4 | | PA4 | ||

| Line 186: | Line 229: | ||

| ADC4 | | ADC4 | ||

| DAC_OUT1 | | DAC_OUT1 | ||

| − | |||

|- | |- | ||

| PA5 | | PA5 | ||

| Line 193: | Line 235: | ||

| | | | ||

| DAC_OUT2 | | DAC_OUT2 | ||

| − | |||

|- | |- | ||

| PA6 | | PA6 | ||

| Line 200: | Line 241: | ||

| TIM3_CH1 | | TIM3_CH1 | ||

| | | | ||

| − | |||

|- | |- | ||

| PA7 | | PA7 | ||

| Line 207: | Line 247: | ||

| TIM3_CH2 | | TIM3_CH2 | ||

| | | | ||

| − | |||

|- | |- | ||

| PA8 | | PA8 | ||

| Line 214: | Line 253: | ||

| MCO | | MCO | ||

| | | | ||

| − | |||

|- | |- | ||

| '''PA9''' | | '''PA9''' | ||

| Line 221: | Line 259: | ||

| | | | ||

| | | | ||

| − | |||

|- | |- | ||

| '''PA10''' | | '''PA10''' | ||

| Line 228: | Line 265: | ||

| | | | ||

| | | | ||

| − | |||

|- | |- | ||

| PA11 | | PA11 | ||

| Line 235: | Line 271: | ||

| TIM1_CH4 | | TIM1_CH4 | ||

| USBDM | | USBDM | ||

| − | |||

|- | |- | ||

| PA12 | | PA12 | ||

| Line 242: | Line 277: | ||

| TIM1_ETR | | TIM1_ETR | ||

| USBDP | | USBDP | ||

| − | |||

|- | |- | ||

| ''PA13'' | | ''PA13'' | ||

| Line 249: | Line 283: | ||

| | | | ||

| | | | ||

| − | |||

|- | |- | ||

| ''PA14'' | | ''PA14'' | ||

| Line 256: | Line 289: | ||

| | | | ||

| | | | ||

| − | |||

|- | |- | ||

| ''PA15'' | | ''PA15'' | ||

| Line 263: | Line 295: | ||

| SPI1_NSS | | SPI1_NSS | ||

| | | | ||

| − | |||

|} | |} | ||

| Line 274: | Line 305: | ||

! Function 3 | ! Function 3 | ||

! Function 4 | ! Function 4 | ||

| − | |||

|- | |- | ||

| PB0 | | PB0 | ||

| Line 281: | Line 311: | ||

| | | | ||

| | | | ||

| − | |||

|- | |- | ||

| PB1 | | PB1 | ||

| Line 288: | Line 317: | ||

| | | | ||

| | | | ||

| − | |||

|- | |- | ||

| '''PB2''' | | '''PB2''' | ||

| Line 295: | Line 323: | ||

| | | | ||

| | | | ||

| − | |||

|- | |- | ||

| PB3 | | PB3 | ||

| Line 302: | Line 329: | ||

| SPI1_SCK | | SPI1_SCK | ||

| | | | ||

| − | |||

|- | |- | ||

| ''PB4'' | | ''PB4'' | ||

| Line 309: | Line 335: | ||

| SPI1_MISO | | SPI1_MISO | ||

| | | | ||

| − | |||

|- | |- | ||

| PB5 | | PB5 | ||

| Line 316: | Line 341: | ||

| SPI1_MOSI | | SPI1_MOSI | ||

| | | | ||

| − | |||

|- | |- | ||

| PB6 | | PB6 | ||

| Line 323: | Line 347: | ||

| USART1_TX | | USART1_TX | ||

| | | | ||

| − | |||

|- | |- | ||

| PB7 | | PB7 | ||

| Line 330: | Line 353: | ||

| USART1_RX | | USART1_RX | ||

| | | | ||

| − | |||

|- | |- | ||

| PB8 | | PB8 | ||

| Line 337: | Line 359: | ||

| CANRX | | CANRX | ||

| SDIO_D4 | | SDIO_D4 | ||

| − | |||

|- | |- | ||

| PB9 | | PB9 | ||

| Line 344: | Line 365: | ||

| CANTX | | CANTX | ||

| SDIO_D5 | | SDIO_D5 | ||

| − | |||

|- | |- | ||

| PB10 | | PB10 | ||

| Line 351: | Line 371: | ||

| TIM2_CH3 | | TIM2_CH3 | ||

| | | | ||

| − | |||

|- | |- | ||

| PB11 | | PB11 | ||

| Line 358: | Line 377: | ||

| TIM2_CH4 | | TIM2_CH4 | ||

| | | | ||

| − | |||

|- | |- | ||

| PB12 | | PB12 | ||

| Line 365: | Line 383: | ||

| USART3_CK | | USART3_CK | ||

| TIM1_BKIN | | TIM1_BKIN | ||

| − | |||

|- | |- | ||

| PB13 | | PB13 | ||

| Line 372: | Line 389: | ||

| TIM1_CH1N | | TIM1_CH1N | ||

| | | | ||

| − | |||

|- | |- | ||

| PB14 | | PB14 | ||

| Line 379: | Line 395: | ||

| TIM1_CH2N | | TIM1_CH2N | ||

| | | | ||

| − | |||

|- | |- | ||

| PB15 | | PB15 | ||

| Line 386: | Line 401: | ||

| | | | ||

| | | | ||

| − | |||

|} | |} | ||

| Line 395: | Line 409: | ||

! Function 1 | ! Function 1 | ||

! Function 2 | ! Function 2 | ||

| − | |||

|- | |- | ||

| PC0 | | PC0 | ||

| ADC10 | | ADC10 | ||

| | | | ||

| − | |||

|- | |- | ||

| PC1 | | PC1 | ||

| ADC11 | | ADC11 | ||

| | | | ||

| − | |||

|- | |- | ||

| PC2 | | PC2 | ||

| ADC12 | | ADC12 | ||

| | | | ||

| − | |||

|- | |- | ||

| PC3 | | PC3 | ||

| ADC13 | | ADC13 | ||

| | | | ||

| − | |||

|- | |- | ||

| PC4 | | PC4 | ||

| ADC14 | | ADC14 | ||

| | | | ||

| − | |||

|- | |- | ||

| PC5 | | PC5 | ||

| ADC15 | | ADC15 | ||

| | | | ||

| − | |||

|- | |- | ||

| PC6 | | PC6 | ||

| TIM3_CH1 | | TIM3_CH1 | ||

| SDIO_D6 | | SDIO_D6 | ||

| − | |||

|- | |- | ||

| PC7 | | PC7 | ||

| TIM3_CH2 | | TIM3_CH2 | ||

| SDIO_D7 | | SDIO_D7 | ||

| − | |||

|- | |- | ||

| PC8 | | PC8 | ||

| TIM3_CH3 | | TIM3_CH3 | ||

| SDIO_D0 | | SDIO_D0 | ||

| − | |||

|- | |- | ||

| PC9 | | PC9 | ||

| TIM3_CH4 | | TIM3_CH4 | ||

| SDIO_D1 | | SDIO_D1 | ||

| − | |||

|- | |- | ||

| PC10 | | PC10 | ||

| USART3_TX | | USART3_TX | ||

| SDIO_D2 | | SDIO_D2 | ||

| − | |||

|- | |- | ||

| PC11 | | PC11 | ||

| USART3_RX | | USART3_RX | ||

| SDIO_D3 | | SDIO_D3 | ||

| − | |||

|- | |- | ||

| PC12 | | PC12 | ||

| USART3_CK | | USART3_CK | ||

| SDIO_CK | | SDIO_CK | ||

| − | |||

|- | |- | ||

| PC13 | | PC13 | ||

| TAMPER-RTC | | TAMPER-RTC | ||

| | | | ||

| − | |||

|- | |- | ||

| '''PC14''' | | '''PC14''' | ||

| '''OSC32_IN''' | | '''OSC32_IN''' | ||

| | | | ||

| − | |||

|- | |- | ||

| '''PC15''' | | '''PC15''' | ||

| '''OSC32_OUT''' | | '''OSC32_OUT''' | ||

| | | | ||

| − | |||

|} | |} | ||

| Line 484: | Line 481: | ||

! Function 1 | ! Function 1 | ||

! Function 2 | ! Function 2 | ||

| − | |||

|- | |- | ||

| '''PD0''' | | '''PD0''' | ||

| '''OSC_IN''' | | '''OSC_IN''' | ||

| | | | ||

| − | |||

|- | |- | ||

| '''PD1''' | | '''PD1''' | ||

| '''OSC_OUT''' | | '''OSC_OUT''' | ||

| | | | ||

| − | |||

|- | |- | ||

| PD2 | | PD2 | ||

| TIM3_ETR | | TIM3_ETR | ||

| SDIO_CMD | | SDIO_CMD | ||

| − | |||

|} | |} | ||

| Line 839: | Line 832: | ||

| | | | ||

| Alternate Function | | Alternate Function | ||

| + | |} | ||

| + | |- | ||

| + | | RCC_AHBENR | ||

| + | | AHB peripheral clock enable register | ||

| + | | Setting any of these bits to 1 enables the clock to by passed to the selected device and allow its settings registers to be set<br /> | ||

| + | If using an alternate function (for SDIO) on any pin of any port, the alternate function clock enable bit must be set | ||

| + | {| class="wikitable" border="1" cellspacing="0" | ||

| + | ! [31:11] | ||

| + | ! 10 | ||

| + | ! 9 | ||

| + | ! 8 | ||

| + | ! 7 | ||

| + | ! 6 | ||

| + | ! 5 | ||

| + | ! 4 | ||

| + | ! 3 | ||

| + | ! 2 | ||

| + | ! 1 | ||

| + | ! 0 | ||

| + | |- | ||

| + | | | ||

| + | | SDIO EN | ||

| + | | | ||

| + | | SMC EN | ||

| + | | | ||

| + | | CRCE N | ||

| + | | | ||

| + | | FLITF EN | ||

| + | | | ||

| + | | SRAM EN | ||

| + | | DMA2 EN | ||

| + | | DMA1 EN | ||

|} | |} | ||

|} | |} | ||

Latest revision as of 07:33, 31 January 2014

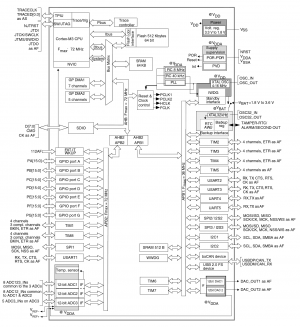

Key features of the STM32F103RET6 microcontroller

Contents

Overview

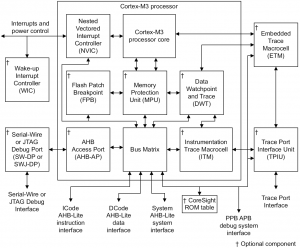

- Core: ARM 32-bit CortexTM-M3 CPU

- 72 MHz maximum frequency, 1.25 DMIPS/MHz (Dhrystone 2.1) performance at 0 wait state memory access

- Single-cycle multiplication and hardware division

- Memories

- 256 to 512 Kbytes of Flash memory

- up to 64 Kbytes of SRAM

- Flexible static memory controller with 4 Chip Select. Supports Compact Flash, SRAM, PSRAM, NOR and NAND memories

- LCD parallel interface, 8080/6800 modes

- Clock, reset and supply management

- 2.0 to 3.6 V application supply and I/Os

- POR, PDR, and programmable voltage detector (PVD)

- 4-to-16 MHz crystal oscillator

- Internal 8 MHz factory-trimmed RC

- Internal 40 kHz RC with calibration

- 32 kHz oscillator for RTC with calibration

- Low power

- Sleep, Stop and Standby modes

- VBAT supply for RTC and backup registers

- 3 × 12-bit, 1 μs A/D converters (up to 21 channels)

- Conversion range: 0 to 3.6 V

- Triple-sample and hold capability

- Temperature sensor

- 2 × 12-bit D/A converters

- DMA: 12-channel DMA controller

- Supported peripherals: timers, ADCs, DAC, SDIO, I2Ss, SPIs, I2Cs and USARTs

- Debug mode

- Serial wire debug (SWD) & JTAG interfaces

- Cortex-M3 Embedded Trace MacrocellTM

- Up to 112 fast I/O ports

- 51/80/112 I/Os, all mappable on 16 external interrupt vectors and almost all 5 V-tolerant

- Up to 11 timers

- Up to four 16-bit timers, each with up to 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input

- 2 × 16-bit motor control PWM timers with dead-time generation and emergency stop

- 2 × watchdog timers (Independent and Window)

- SysTick timer: a 24-bit downcounter

- 2 × 16-bit basic timers to drive the DAC

- Up to 13 communication interfaces

- Up to 2 × I2C interfaces (SMBus/PMBus)

- Up to 5 USARTs (ISO 7816 interface, LIN, IrDA capability, modem control)

- Up to 3 SPIs (18 Mbit/s), 2 with I2S interface multiplexed

- CAN interface (2.0B Active)

- USB 2.0 full speed interface

- SDIO interface

- CRC calculation unit, 96-bit unique ID

- ECOP ACK® packages

Documents and files

- ARM: Cortex-M3 Thumb-2 instruction set

- STM32 resources (Look in "Design support/SW DEMOS" for the Flash upload tool)

- Reference Manual

- Specifications

- Programming Manual

- Latest version of Keil µVision (Register for free to get the download link)

- Futurlec STM32 Stamp product page

Power saving levels

- Sleep mode (Cortex-M3 core stopped, peripherals kept running)

- Stop mode (all clocks are stopped)

- Standby mode (1.8V domain powered-off)

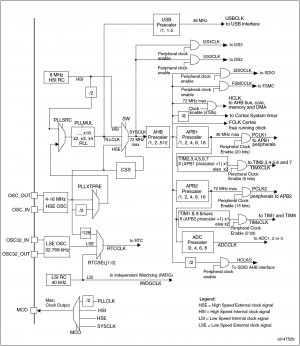

Clocks

HSI (8 MHz internal RC oscillator) HSE (8 MHz external crystal oscillator) LSI (40 kHz internal RC - watchdog, RTCCLK) LSE (32768 Hz external crystal (RTCCLK)) PLLCLK - Output from PLL, 8-64 MHz in 4 MHz steps, 72-128 MHz in 8 MHz steps SYSCLK - PLLCLK, HSI or HSE AHBCLK - SYSCLK / AHB prescaler (this clock has no name in the datasheet, except AHB peripheral clock) PCLK1 - AHBCLK / APB1 prescaler - APB1 bus (max 36 MHz) PCLK2 - AHBCLK / APB2 prescaler - APB2 bus (max 72 MHz) USBCLK - PLLCLK / USB prescaler I2SCLK - SYSCLK SDIOCLK - AHBCLK FSMCCLK - AHBCLK FCLK - AHBCLK ADCCLK - AHBCLK / (APB2 prescaler * ADC prescaler)

- The MCO pin (PA8) can output one of SYSCLK, HSI, HSE, PLLCLK / 2

- When the HSI is the PLL clock input, maximum system clock frequency is 64 MHz.

- The SDIO AHB interface is clocked with a fixed frequency equal to AHBCLK / 2.

- If the APB prescaler is 1, timers run at PCLK else at 2 * PCLK

Flash memory

- 0-24 MHz - zero wait state

- 24-48 MHz - one wait state

- 48-72 MHz - two wait states

The prefetch buffer must be switched on/off only when SYSCLOCK is lower than 24 MHz.

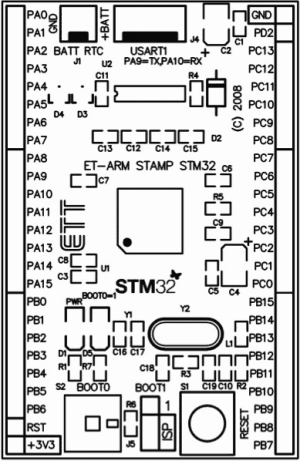

Pins with special functions

PA9 ----------> ICL3232 PA10 <--|100R|-- ICL3232 PB2 - Boot1 22 kOhm to +3.3 V or Gnd PC14 - 32 kHz crystal PC15 - 32 kHz crystal PD0 - 8 MHz crystal PD1 - 8 MHz crystal The JTAG pins are in input PU/PD after reset: PA15: JTDI in PU PA14: JTCK in PD PA13: JTMS in PU PB4: NJTRST in PU

Peripherials

64 kB SRAM, 512 kB FLASH

3 x 12 bit A/D converters

2 x 12 bit D/A converters

5 x USART

2 x Advanced-control timers (TIM1 and TIM8) can each be seen as a three-phase PWM multiplexed on 6 channels.

4 x General purpose timer TIM2, TIM3, TIM4 and TIM5 - 16-bit auto-reload up/down counter,

a 16-bit prescaler and feature 4 independent channels each for input capture/output compare,

PWM or onepulse mode output. This gives up to 16 input captures / output compares / PWMs

2 x Basic timer TIM6 and TIM7 - These timers are mainly used for DAC trigger generation.

They can also be used as a generic 16-bit time base.

3 x SPI

2 x I2S (multiplexed on SPI pins)

2 × I2C

1 x SD card interface 1/4/8 bit

1 x USB full speed

1 x CAN network interface

1 x CRC (cyclic redundancy check) calculation unit

1 x 24 bit systick timer

1 x RTC (real-time clock) and backup registers

2 x DMA controller, 5 + 7 channels

1 x Temperature sensor

A/D converters

- Three 12 bit A/D converters at 1 MHz (2 MHz when running ADC1 and ADC2 in interleave)

- ADC1_IN17 is connected to VREFINT 1.2 V (1.16 V - 1.24 V)

- ADC1_IN16 is connected to the Temperature sensor

- ADC2_IN16 and ADC2_IN17 are connected to VSS

- ADC3_IN9, ADC3_IN14, ADC3_IN15, ADC3_IN16 and ADC3_IN17 are connected to VSS

The recommended sampling time for the internal channels is 17.1 μs. The TSVREFE bit must be set to enable both internal channels.

D/A converters

- Two 12 bit D/A converters, 1 MHz

- Minimum load resistance with buffer enabled, 5 kOhm

- Minumum load resistance with buffer disabled, 1.5 MOhm

- Capacitive load with buffer enabled, 50 pF

DMA controllers

Two DMA controllers with 7 and 5 channels. Data can be transferred from any address to any address, with or without increment. The CPU core is guaranteed 50% of the bus capacity so DMA will never cause the CPU to hang.

Timers

| IWDG | Independent watchdog down counter. 12 bit with 8 bit prescaler, clocked by LSI (40 kHz). Reset when reaching 0. |

| WWDG | Window watchdog, clocked by PCLK1 through WDG prescaler |

| SYSTICK | Independent 24 bit timer within the ARM core |

| TIMER1 and TIMER8 | Advanced-control 16 bit timers with quadrature and hall-sensor support |

| TIMER2 to TIMER5 | 16 bit general purpose timers |

| TIMER6 and TIMER7 | Basic 16 bit timers mainly used to drive the DAC |

- If the APB prescaler is 1, peripheral timers run at PCLK else at 2 * PCLK

Flash uploader

Command line parameters for STMFlashLoader.exe:

-c --pn 3 --br 115200 --db 8 --sb 1 --to 1000 -i "STM32_High-density_512K" -e --all -d --fn "#H"

--pn 3 indicates com port: COM3

Important things to remember

- Registers need a clock to latch the data, so enable all the the upstream clocks before trying to configure a peripheral. See RCC_APB1ENR and RCC_APB2ENR under Registers

- Pins with special functions

- Alternate function bit (AFIO) must be set if using anything other than GPIO on any port. See RCC_APB2ENR under Registers

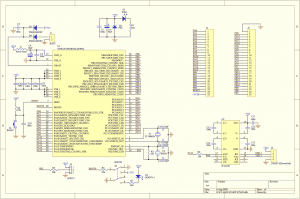

Pinout

- Bold items represent pins with special functions

- Italic items represent pins that are configured in JTAG mode on power up/reset

- All pins without a special function can be used as general purpose digital Input or Output (GPIO)

- Warning: do not set special function pins in output mode without consulting the stamp schematic

- Pins are 5V tolerant

| Pin | Function 1 | Function 2 | Function 3 | Function 4 |

|---|---|---|---|---|

| PA0 | WKUP | USART2_CTS | ADC0 | TIM2_CH1_ETR |

| PA1 | USART2_RTS | ADC1 | TIM2_CH2 | |

| PA2 | USART2_TX | ADC2 | TIM2_CH3 | |

| PA3 | USART2_RX | ADC3 | TIM2_CH4 | |

| PA4 | SPI1_NSS | USART2_CK | ADC4 | DAC_OUT1 |

| PA5 | SPI1_SCK | ADC5 | DAC_OUT2 | |

| PA6 | SPI1_MISO | ADC6 | TIM3_CH1 | |

| PA7 | SPI1_MOSI | ADC7 | TIM3_CH2 | |

| PA8 | USART1_CK | TIM1_CH1 | MCO | |

| PA9 | USART1_TX | TIM1_CH2 | ||

| PA10 | USART1_RX | TIM1_CH3 | ||

| PA11 | USART1_CTS | CANRX | TIM1_CH4 | USBDM |

| PA12 | USART1_RTS | CANTX | TIM1_ETR | USBDP |

| PA13 | JTMS | SWDIO | ||

| PA14 | JTCK | SWCLK | ||

| PA15 | JTDI | TIM2_CH1 | SPI1_NSS |

| Pin | Function 1 | Function 2 | Function 3 | Function 4 |

|---|---|---|---|---|

| PB0 | ADC8 | TIM3_CH3 | ||

| PB1 | ADC9 | IM3_CH4 | ||

| PB2 | BOOT1 | |||

| PB3 | JTDO | TIM2_CH2 | SPI1_SCK | |

| PB4 | JNTRST | TIM3_CH1 | SPI1_MISO | |

| PB5 | I2C1_SMBAI | TIM3_CH2 | SPI1_MOSI | |

| PB6 | I2C1_SCL | TIM4_CH1 | USART1_TX | |

| PB7 | I2C1_SDA | TIM4_CH2 | USART1_RX | |

| PB8 | TIM4_CH3 | I2C1_SCL | CANRX | SDIO_D4 |

| PB9 | TIM4_CH4 | I2C1_SDA | CANTX | SDIO_D5 |

| PB10 | I2C2_SCL | USART3_TX | TIM2_CH3 | |

| PB11 | I2C2_SDA | USART3_RX | TIM2_CH4 | |

| PB12 | SPI2_NSS | I2C2_SMBAI | USART3_CK | TIM1_BKIN |

| PB13 | SPI2_SCK | USART3_CTS | TIM1_CH1N | |

| PB14 | SPI2_MISO | USART3_RTS | TIM1_CH2N | |

| PB15 | SPI2_MOSI | TIM1_CH3N |

| Pin | Function 1 | Function 2 |

|---|---|---|

| PC0 | ADC10 | |

| PC1 | ADC11 | |

| PC2 | ADC12 | |

| PC3 | ADC13 | |

| PC4 | ADC14 | |

| PC5 | ADC15 | |

| PC6 | TIM3_CH1 | SDIO_D6 |

| PC7 | TIM3_CH2 | SDIO_D7 |

| PC8 | TIM3_CH3 | SDIO_D0 |

| PC9 | TIM3_CH4 | SDIO_D1 |

| PC10 | USART3_TX | SDIO_D2 |

| PC11 | USART3_RX | SDIO_D3 |

| PC12 | USART3_CK | SDIO_CK |

| PC13 | TAMPER-RTC | |

| PC14 | OSC32_IN | |

| PC15 | OSC32_OUT |

| Pin | Function 1 | Function 2 |

|---|---|---|

| PD0 | OSC_IN | |

| PD1 | OSC_OUT | |

| PD2 | TIM3_ETR | SDIO_CMD |

Programming

Registers

- note [y:x] refers to all bits in a register from bit x to bit y (inclusive)

| Register | Name | Description | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| GPIOx_ODR | Output Data Register | sets the pins bit-state to that of the bits in this register, but only those pins configured in output mode

x denotes the port name, A to G, however, the stamp module only provides ports A to D | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| GPIOx_IDR | Input Data Register | reads the pins bit-state to that of the logic level applied to the pins

x denotes the port name, A to G, however, the stamp module only provides ports A to D | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| GPIOx_BSRR | Port bit set/reset register | sets or resets(un-sets) particular pins while leaving all other pins in their current state

if set and reset are both set, set has priority

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| GPIOx_CRL | Port configuration register low | sets pin modes, function, speed, and direction for pins 0-7

x denotes the port name, A to G, however, the stamp module only provides ports A to D

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| GPIOx_CRH | Port configuration register high | sets pin modes, function, speed, and direction for pins 8-15

x denotes the port number, A to G, however, the stamp module only provides ports A to D

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| RCC_APB1ENR | APB1 peripheral clock enable register | Setting any of these bits to 1 enables the clock to by passed to the selected peripheral and allow its settings registers to be set

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| RCC_APB2ENR | APB2 peripheral clock enable register | Setting any of these bits to 1 enables the clock to by passed to the selected peripheral and allow its settings registers to be set If using an alternate function on any pin of any port, the alternate function clock enable bit must be set

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| RCC_AHBENR | AHB peripheral clock enable register | Setting any of these bits to 1 enables the clock to by passed to the selected device and allow its settings registers to be set If using an alternate function (for SDIO) on any pin of any port, the alternate function clock enable bit must be set

|