Difference between revisions of "STM32F407 Microcontroller"

(→Pinout) |

(→Programming) |

||

| (53 intermediate revisions by 2 users not shown) | |||

| Line 36: | Line 36: | ||

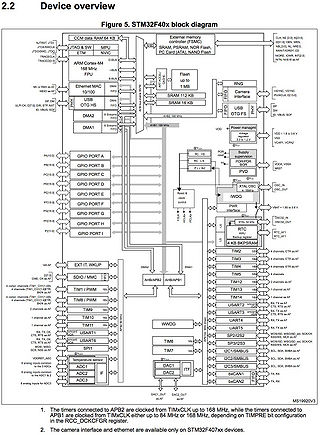

Each main block of memory is on a different layer of the bus matrix and can be accessed independently by CPU core or DMA. | Each main block of memory is on a different layer of the bus matrix and can be accessed independently by CPU core or DMA. | ||

| − | + | Embedded Flash | |

| − | Name | + | '''Name Address Size Bus* Description''' |

| − | OTP 512 | + | Main 0x0800 0000 1MB ID Sectors: 4 x 16KB, 1 x 64KB, 7 x 128KB |

| + | System 0x1FFF 0000 30KB ID Bootloader | ||

| + | OTP 0x1FFF 7800 528B ID 512 Bytes of one-time programmable memory for user data and 16 lock bytes | ||

| + | Option 0x1FFF C000 16B ID Configuration of read and write protection, BOR level, watchdog, software/hardware and reset | ||

SRAM | SRAM | ||

| − | Name | + | '''Name Address Size Bus Description''' |

| − | SRAM1 | + | SRAM1 0x2000 0000 112KB IDS Main internal SRAM |

| − | SRAM2 | + | SRAM2 0x2001 C000 16KB S Auxiliary internal SRAM |

| − | CCM | + | CCM 0x1000 0000 64KB D Core coupled memory ( only accessible by CPU ) |

| − | BKPSRAM | + | BKPSRAM 0x4002 4000 4KB S Backup SRAM ( Battery backup domain ) |

| − | FSMC | + | FSMC B1 0x6000 0000 256MB IDS NOR / PSRAM ( Flexible static memory controller (External memory) ) |

| + | FSMC B2 0x7000 0000 256MB IDS NAND Flash | ||

| + | FSMC B3 0x8000 0000 256MB IDS NAND Flash | ||

| + | FSMC B4 0x9000 0000 256MB IDS PC Card | ||

| + | |||

| + | '''*'''I = Instruction bus, D = Data bus, S = System bus | ||

=== Pin functions === | === Pin functions === | ||

| Line 310: | Line 318: | ||

| bgcolor="#FFFFFF" | SPI3_NSS | | bgcolor="#FFFFFF" | SPI3_NSS | ||

| bgcolor="#FFFFFF" | I2S3_WS | | bgcolor="#FFFFFF" | I2S3_WS | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | TIM2_CH1_ETR |

| bgcolor="#FFFFFF" | SPI1_NSS | | bgcolor="#FFFFFF" | SPI1_NSS | ||

| bgcolor="#FFFFFF" | EVENTOUT | | bgcolor="#FFFFFF" | EVENTOUT | ||

| Line 2,010: | Line 2,018: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | OTG_HS_ULPI_STP | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PC1 | | bgcolor="#FFFFFF" | PC1 | ||

| Line 2,029: | Line 2,037: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | ETH_MDC | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PC2 | | bgcolor="#FFFFFF" | PC2 | ||

| Line 2,041: | Line 2,049: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SPI2_MISO | ||

| + | | bgcolor="#FFFFFF" | I2S2ext_SD | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | OTG_HS_ULPI_DIR | ||

| + | | bgcolor="#FFFFFF" | ETH _MII_TXD2 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PC3 | | bgcolor="#FFFFFF" | PC3 | ||

| Line 2,059: | Line 2,067: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SPI2_MOSI<br />I2S2_SD | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | OTG_HS_ULPI_NXT | ||

| + | | bgcolor="#FFFFFF" | ETH_MII_TX_CLK | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PC4 | | bgcolor="#FFFFFF" | PC4 | ||

| Line 2,083: | Line 2,091: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | ETH_MII_RXD0<br />ETH_RMII_RXD0 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PC5 | | bgcolor="#FFFFFF" | PC5 | ||

| Line 2,101: | Line 2,109: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | ETH _MII_RXD1<br />ETH _RMII_RXD1 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PC6 | | bgcolor="#FFFFFF" | PC6 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM3_CH1 | ||

| + | | bgcolor="#FFFFFF" | TIM8_CH1 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | I2S2_MCK | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | USART6_TX | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SDIO_D6 | ||

| + | | bgcolor="#FFFFFF" | DCMI_D0 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PC7 | | bgcolor="#FFFFFF" | PC7 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM3_CH2 | ||

| + | | bgcolor="#FFFFFF" | TIM8_CH2 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | I2S3_MCK | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | USART6_RX | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SDIO_D7 | ||

| + | | bgcolor="#FFFFFF" | DCMI_D1 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PC8 | | bgcolor="#FFFFFF" | PC8 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM3_CH3 | ||

| + | | bgcolor="#FFFFFF" | TIM8_CH3 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | USART6_CK | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SDIO_D0 | ||

| + | | bgcolor="#FFFFFF" | DCMI_D2 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PC9 | | bgcolor="#FFFFFF" | PC9 | ||

| + | | bgcolor="#FFFFFF" | MCO2 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM3_CH4 | ||

| + | | bgcolor="#FFFFFF" | TIM8_CH4 | ||

| + | | bgcolor="#FFFFFF" | I2C3_SDA | ||

| + | | bgcolor="#FFFFFF" | I2S_CKIN | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,169: | Line 2,182: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SDIO_D1 | ||

| + | | bgcolor="#FFFFFF" | DCMI_D3 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PC10 | | bgcolor="#FFFFFF" | PC10 | ||

| Line 2,186: | Line 2,194: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SPI3_SCK<br />I2S3_CK | ||

| + | | bgcolor="#FFFFFF" | USART3_TX | ||

| + | | bgcolor="#FFFFFF" | UART4_TX | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SDIO_D2 | ||

| + | | bgcolor="#FFFFFF" | DCMI_D8 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PC11 | | bgcolor="#FFFFFF" | PC11 | ||

| Line 2,203: | Line 2,211: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | I2S3ext_SD | ||

| + | | bgcolor="#FFFFFF" | SPI3_MISO | ||

| + | | bgcolor="#FFFFFF" | USART3_RX | ||

| + | | bgcolor="#FFFFFF" | UART4_RX | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SDIO_D3 | ||

| + | | bgcolor="#FFFFFF" | DCMI_D4 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PC12 | | bgcolor="#FFFFFF" | PC12 | ||

| Line 2,222: | Line 2,230: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SPI3_MOSI<br />I2S3_SD | ||

| + | | bgcolor="#FFFFFF" | USART3_CK | ||

| + | | bgcolor="#FFFFFF" | UART5_TX | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SDIO_CK | ||

| + | | bgcolor="#FFFFFF" | DCMI_D9 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PC13 | | bgcolor="#FFFFFF" | PC13 | ||

| Line 2,249: | Line 2,257: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

|- | |- | ||

| bgcolor="#FFFFFF" | PC14 | | bgcolor="#FFFFFF" | PC14 | ||

| Line 2,267: | Line 2,275: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

|- | |- | ||

| bgcolor="#FFFFFF" | PC15 | | bgcolor="#FFFFFF" | PC15 | ||

| Line 2,285: | Line 2,293: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

|- | |- | ||

| bgcolor="#F0F0F0" | PD0 | | bgcolor="#F0F0F0" | PD0 | ||

| Line 2,297: | Line 2,305: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | CAN1_RX | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_D2 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD1 | | bgcolor="#F0F0F0" | PD1 | ||

| Line 2,315: | Line 2,323: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | CAN1_TX | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_D3 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD2 | | bgcolor="#F0F0F0" | PD2 | ||

| Line 2,332: | Line 2,340: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | UART5_RX | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | SDIO_CMD | ||

| + | | bgcolor="#F0F0F0" | DCMI_D11 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD3 | | bgcolor="#F0F0F0" | PD3 | ||

| Line 2,349: | Line 2,357: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | USART2_CTS | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_CLK | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD4 | | bgcolor="#F0F0F0" | PD4 | ||

| Line 2,367: | Line 2,375: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | USART2_RTS | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_NOE | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD5 | | bgcolor="#F0F0F0" | PD5 | ||

| Line 2,385: | Line 2,393: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | USART2_TX | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_NWE | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD6 | | bgcolor="#F0F0F0" | PD6 | ||

| Line 2,403: | Line 2,411: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | USART2_RX | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_NWAIT | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD7 | | bgcolor="#F0F0F0" | PD7 | ||

| Line 2,421: | Line 2,429: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | USART2_CK | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_NE1<br />FSMC_NCE2 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD8 | | bgcolor="#F0F0F0" | PD8 | ||

| Line 2,439: | Line 2,447: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | USART3_TX | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_D13 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD9 | | bgcolor="#F0F0F0" | PD9 | ||

| Line 2,457: | Line 2,465: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | USART3_RX | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_D14 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD10 | | bgcolor="#F0F0F0" | PD10 | ||

| Line 2,475: | Line 2,483: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | USART3_CK | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_D15 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD11 | | bgcolor="#F0F0F0" | PD11 | ||

| Line 2,493: | Line 2,501: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | USART3_CTS | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_A16 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD12 | | bgcolor="#F0F0F0" | PD12 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM4_CH1 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | USART3_RTS | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_A17 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD13 | | bgcolor="#F0F0F0" | PD13 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM4_CH2 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 2,533: | Line 2,542: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_A18 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD14 | | bgcolor="#F0F0F0" | PD14 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM4_CH3 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 2,551: | Line 2,560: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_D0 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD15 | | bgcolor="#F0F0F0" | PD15 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM4_CH4 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 2,569: | Line 2,578: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_D1 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE0 | | bgcolor="#FFFFFF" | PE0 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM4_ETR | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,587: | Line 2,596: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_NBL0 | ||

| + | | bgcolor="#FFFFFF" | DCMI_D2 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE1 | | bgcolor="#FFFFFF" | PE1 | ||

| Line 2,606: | Line 2,614: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_NBL1 | ||

| + | | bgcolor="#FFFFFF" | DCMI_D3 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE2 | | bgcolor="#FFFFFF" | PE2 | ||

| + | | bgcolor="#FFFFFF" | TRACECLK | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,622: | Line 2,631: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | ETH _MII_TXD3 | ||

| + | | bgcolor="#FFFFFF" | FSMC_A23 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE3 | | bgcolor="#FFFFFF" | PE3 | ||

| + | | bgcolor="#FFFFFF" | TRACED0 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,641: | Line 2,650: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_A19 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE4 | | bgcolor="#FFFFFF" | PE4 | ||

| + | | bgcolor="#FFFFFF" | TRACED1 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,659: | Line 2,668: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_A20 | ||

| + | | bgcolor="#FFFFFF" | DCMI_D4 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE5 | | bgcolor="#FFFFFF" | PE5 | ||

| + | | bgcolor="#FFFFFF" | TRACED2 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM9_CH1 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,676: | Line 2,686: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_A21 | ||

| + | | bgcolor="#FFFFFF" | DCMI_D6 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE6 | | bgcolor="#FFFFFF" | PE6 | ||

| + | | bgcolor="#FFFFFF" | TRACED3 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM9_CH2 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,694: | Line 2,704: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_A22 | ||

| + | | bgcolor="#FFFFFF" | DCMI_D7 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE7 | | bgcolor="#FFFFFF" | PE7 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM1_ETR | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,713: | Line 2,722: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_D4 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE8 | | bgcolor="#FFFFFF" | PE8 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | IM1_CH1N | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,731: | Line 2,740: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_D5 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE9 | | bgcolor="#FFFFFF" | PE9 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM1_CH1 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,749: | Line 2,758: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_D6 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE10 | | bgcolor="#FFFFFF" | PE10 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM1_CH2N | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,767: | Line 2,776: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_D7 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE11 | | bgcolor="#FFFFFF" | PE11 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM1_CH2 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,785: | Line 2,794: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_D8 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE12 | | bgcolor="#FFFFFF" | PE12 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM1_CH3N | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,803: | Line 2,812: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_D9 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE13 | | bgcolor="#FFFFFF" | PE13 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM1_CH3 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,821: | Line 2,830: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_D10 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE14 | | bgcolor="#FFFFFF" | PE14 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM1_CH4 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,839: | Line 2,848: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_D11 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE15 | | bgcolor="#FFFFFF" | PE15 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM1_BKIN | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 2,857: | Line 2,866: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_D12 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF0 | | bgcolor="#F0F0F0" | PF0 | ||

| Line 2,868: | Line 2,876: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | I2C2_SDA | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 2,875: | Line 2,884: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_A0 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF1 | | bgcolor="#F0F0F0" | PF1 | ||

| Line 2,886: | Line 2,894: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | I2C2_SCL | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 2,893: | Line 2,902: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_A1 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF2 | | bgcolor="#F0F0F0" | PF2 | ||

| Line 2,904: | Line 2,912: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | 2C2_SMBA | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 2,911: | Line 2,920: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_A2 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF3 | | bgcolor="#F0F0F0" | PF3 | ||

| Line 2,930: | Line 2,938: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_A3 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF4 | | bgcolor="#F0F0F0" | PF4 | ||

| Line 2,948: | Line 2,956: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_A4 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF5 | | bgcolor="#F0F0F0" | PF5 | ||

| Line 2,966: | Line 2,974: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_A5 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF6 | | bgcolor="#F0F0F0" | PF6 | ||

| Line 2,975: | Line 2,983: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM10_CH1 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 2,983: | Line 2,992: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_NIORD | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF7 | | bgcolor="#F0F0F0" | PF7 | ||

| Line 2,993: | Line 3,001: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM11_CH1 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 3,001: | Line 3,010: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_NREG | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF8 | | bgcolor="#F0F0F0" | PF8 | ||

| Line 3,017: | Line 3,025: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM13_CH1 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_NIOWR | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF9 | | bgcolor="#F0F0F0" | PF9 | ||

| Line 3,035: | Line 3,043: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM14_CH1 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_CD | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF10 | | bgcolor="#F0F0F0" | PF10 | ||

| Line 3,056: | Line 3,064: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_INTR | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF11 | | bgcolor="#F0F0F0" | PF11 | ||

| Line 3,075: | Line 3,083: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | DCMI_D12 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF12 | | bgcolor="#F0F0F0" | PF12 | ||

| Line 3,092: | Line 3,100: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_A6 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF13 | | bgcolor="#F0F0F0" | PF13 | ||

| Line 3,110: | Line 3,118: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_A7 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF14 | | bgcolor="#F0F0F0" | PF14 | ||

| Line 3,128: | Line 3,136: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_A8 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PF15 | | bgcolor="#F0F0F0" | PF15 | ||

| Line 3,145: | Line 3,153: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | FSMC_A9 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG0 | | bgcolor="#FFFFFF" | PG0 | ||

| Line 3,164: | Line 3,172: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_A10 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG1 | | bgcolor="#FFFFFF" | PG1 | ||

| Line 3,182: | Line 3,190: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_A11 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG2 | | bgcolor="#FFFFFF" | PG2 | ||

| Line 3,200: | Line 3,208: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_A12 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG3 | | bgcolor="#FFFFFF" | PG3 | ||

| Line 3,218: | Line 3,226: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_A13 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG4 | | bgcolor="#FFFFFF" | PG4 | ||

| Line 3,236: | Line 3,244: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_A14 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG5 | | bgcolor="#FFFFFF" | PG5 | ||

| Line 3,254: | Line 3,262: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_A15 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG6 | | bgcolor="#FFFFFF" | PG6 | ||

| Line 3,272: | Line 3,280: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_INT2 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG7 | | bgcolor="#FFFFFF" | PG7 | ||

| Line 3,286: | Line 3,294: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | USART6_CK | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_INT3 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG8 | | bgcolor="#FFFFFF" | PG8 | ||

| Line 3,304: | Line 3,312: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | USART6_RTS | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | ETH _PPS_OUT | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG9 | | bgcolor="#FFFFFF" | PG9 | ||

| Line 3,322: | Line 3,330: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | USART6_RX | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_NE2<br />FSMC_NCE3 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG10 | | bgcolor="#FFFFFF" | PG10 | ||

| Line 3,344: | Line 3,352: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_NCE4_1<br />FSMC_NE3 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG11 | | bgcolor="#FFFFFF" | PG11 | ||

| Line 3,361: | Line 3,369: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | ETH _MII_TX_EN<br />ETH _RMII_TX_EN | ||

| + | | bgcolor="#FFFFFF" | FSMC_NCE4_2 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG12 | | bgcolor="#FFFFFF" | PG12 | ||

| Line 3,376: | Line 3,384: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | USART6_RTS | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | FSMC_NE4 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG13 | | bgcolor="#FFFFFF" | PG13 | ||

| Line 3,394: | Line 3,402: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | UART6_CTS | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | ETH _MII_TXD0<br />ETH _RMII_TXD0 | ||

| + | | bgcolor="#FFFFFF" | FSMC_A24 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG14 | | bgcolor="#FFFFFF" | PG14 | ||

| Line 3,412: | Line 3,420: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | USART6_TX | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | ETH _MII_TXD1<br />ETH _RMII_TXD1 | ||

| + | | bgcolor="#FFFFFF" | FSMC_A25 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG15 | | bgcolor="#FFFFFF" | PG15 | ||

| Line 3,430: | Line 3,438: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | USART6_CTS | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | DCMI_D13 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PH0 | | bgcolor="#F0F0F0" | PH0 | ||

| Line 3,455: | Line 3,463: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

|- | |- | ||

| bgcolor="#F0F0F0" | PH1 | | bgcolor="#F0F0F0" | PH1 | ||

| Line 3,473: | Line 3,481: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

|- | |- | ||

| bgcolor="#F0F0F0" | PH2 | | bgcolor="#F0F0F0" | PH2 | ||

| Line 3,487: | Line 3,495: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | ETH _MII_CRS | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PH3 | | bgcolor="#F0F0F0" | PH3 | ||

| Line 3,505: | Line 3,513: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | ETH _MII_COL | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PH4 | | bgcolor="#F0F0F0" | PH4 | ||

| Line 3,516: | Line 3,524: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | I2C2_SCL | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 3,521: | Line 3,530: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | OTG_HS_ULPI_NXT | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PH5 | | bgcolor="#F0F0F0" | PH5 | ||

| Line 3,534: | Line 3,542: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | I2C2_SDA | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 3,544: | Line 3,553: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PH6 | | bgcolor="#F0F0F0" | PH6 | ||

| Line 3,552: | Line 3,560: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | I2C2_SMBA | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM12_CH1 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | ETH _MII_RXD2 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PH7 | | bgcolor="#F0F0F0" | PH7 | ||

| Line 3,570: | Line 3,578: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | I2C3_SCL | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 3,576: | Line 3,585: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | ETH _MII_RXD3 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PH8 | | bgcolor="#F0F0F0" | PH8 | ||

| Line 3,588: | Line 3,596: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | I2C3_SDA | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 3,596: | Line 3,605: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | DCMI_HSYNC | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PH9 | | bgcolor="#F0F0F0" | PH9 | ||

| Line 3,606: | Line 3,614: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | I2C3_SMBA | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM12_CH2 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | DCMI_D0 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PH10 | | bgcolor="#F0F0F0" | PH10 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM5_CH1 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 3,632: | Line 3,641: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | DCMI_D1 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PH11 | | bgcolor="#F0F0F0" | PH11 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM5_CH2 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 3,650: | Line 3,659: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | DCMI_D2 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PH12 | | bgcolor="#F0F0F0" | PH12 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM5_CH3 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 3,668: | Line 3,677: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | DCMI_D3 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PH13 | | bgcolor="#F0F0F0" | PH13 | ||

| Line 3,677: | Line 3,685: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM8_CH1N | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 3,682: | Line 3,691: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | CAN1_TX | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 3,687: | Line 3,697: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PH14 | | bgcolor="#F0F0F0" | PH14 | ||

| Line 3,695: | Line 3,703: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM8_CH2N | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 3,704: | Line 3,713: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | DCMI_D4 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PH15 | | bgcolor="#F0F0F0" | PH15 | ||

| Line 3,713: | Line 3,721: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | TIM8_CH3N | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| Line 3,722: | Line 3,731: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| + | | bgcolor="#F0F0F0" | DCMI_D11 | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

| − | | bgcolor="#F0F0F0" | | + | | bgcolor="#F0F0F0" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PI0 | | bgcolor="#FFFFFF" | PI0 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM5_CH4 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SPI2_NSS<br />I2S2_WS | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 3,739: | Line 3,749: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | DCMI_D13 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PI1 | | bgcolor="#FFFFFF" | PI1 | ||

| Line 3,751: | Line 3,759: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SPI2_SCK<br />I2S2_CK | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 3,758: | Line 3,767: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | DCMI_D8 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PI2 | | bgcolor="#FFFFFF" | PI2 | ||

| Line 3,767: | Line 3,775: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM8_CH4 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SPI2_MISO | ||

| + | | bgcolor="#FFFFFF" | I2S2ext_SD | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 3,774: | Line 3,785: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | DCMI_D8 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PI3 | | bgcolor="#FFFFFF" | PI3 | ||

| Line 3,785: | Line 3,793: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM8_ETR | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | SPI2_MOSI<br />I2S2_SD | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 3,793: | Line 3,803: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | DCMI_D8 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PI4 | | bgcolor="#FFFFFF" | PI4 | ||

| Line 3,803: | Line 3,811: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM8_BKIN | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 3,812: | Line 3,821: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | DCMI_D5 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PI5 | | bgcolor="#FFFFFF" | PI5 | ||

| Line 3,821: | Line 3,829: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM8_CH1 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 3,830: | Line 3,839: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | DCMI_VSYNC | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PI6 | | bgcolor="#FFFFFF" | PI6 | ||

| Line 3,839: | Line 3,847: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM8_CH2 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 3,848: | Line 3,857: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | DCMI_D6 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PI7 | | bgcolor="#FFFFFF" | PI7 | ||

| Line 3,857: | Line 3,865: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | TIM8_CH3 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 3,866: | Line 3,875: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | DCMI_D7 | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PI8 | | bgcolor="#FFFFFF" | PI8 | ||

| Line 3,887: | Line 3,895: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

|- | |- | ||

| bgcolor="#FFFFFF" | PI9 | | bgcolor="#FFFFFF" | PI9 | ||

| Line 3,899: | Line 3,907: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | CAN1_RX | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| Line 3,904: | Line 3,913: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PI10 | | bgcolor="#FFFFFF" | PI10 | ||

| Line 3,919: | Line 3,927: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | ETH _MII_RX_ER | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PI11 | | bgcolor="#FFFFFF" | PI11 | ||

| Line 3,936: | Line 3,944: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | | bgcolor="#FFFFFF" | OTG_HS_ULPI_DIR | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | EVENTOUT |

| − | + | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PI12 | | bgcolor="#FFFFFF" | PI12 | ||

| Line 4,014: | Line 4,022: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | |} | ||

| + | |||

| + | ===ADC Mapping=== | ||

| + | {| class="wikitable" border="1" cellspacing="0" | style="text-align:center" | ||

| + | |+ '''ADC channel mapping''' | ||

| + | | '''Channel''' | ||

| + | | '''ADC1''' | ||

| + | | '''ADC2''' | ||

| + | | '''ADC3''' | ||

| + | |- | ||

| + | | '''0''' | ||

| + | | PA0 | ||

| + | | PA0 | ||

| + | | PA0 | ||

| + | |- | ||

| + | | '''1''' | ||

| + | | PA1 | ||

| + | | PA1 | ||

| + | | PA1 | ||

| + | |- | ||

| + | | '''2''' | ||

| + | | PA2 | ||

| + | | PA2 | ||

| + | | PA2 | ||

| + | |- | ||