Difference between revisions of "STM32F429 Microcontroller"

From ScienceZero

(→PCB IO map) |

(→PCB IO map) |

||

| (15 intermediate revisions by 2 users not shown) | |||

| Line 51: | Line 51: | ||

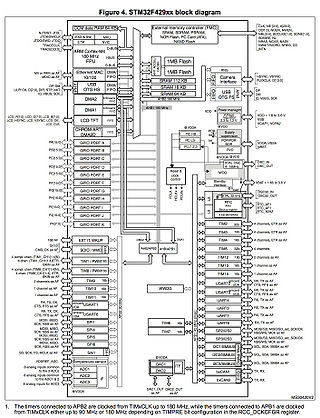

'''STM32F429 clock tree'''<br /> | '''STM32F429 clock tree'''<br /> | ||

[[File:STM32F429_clock_tree.jpg|320px]] | [[File:STM32F429_clock_tree.jpg|320px]] | ||

| + | |||

| + | === Memory map === | ||

| + | SRAM | ||

| + | '''Name Address Size Bus Description''' | ||

| + | SRAM1 0x2000 0000 112KB IDS Main internal SRAM | ||

| + | SRAM2 0x2001 C000 16KB S Auxiliary internal SRAM | ||

| + | SRAM3 0x2002 0000 64KB S Auxiliary internal SRAM | ||

| + | CCM 0x1000 0000 64KB D Core coupled memory ( only accessible by CPU ) | ||

| + | BKPSRAM 0x4002 4000 4KB S Backup SRAM ( Battery backup domain ) | ||

| + | |||

| + | '''*'''I = Instruction bus, D = Data bus, S = System bus | ||

=== Documents and files === | === Documents and files === | ||

| Line 59: | Line 70: | ||

*[http://www.st.com/st-web-ui/static/active/en/resource/technical/document/programming_manual/DM00046982.pdf Programming manual] | *[http://www.st.com/st-web-ui/static/active/en/resource/technical/document/programming_manual/DM00046982.pdf Programming manual] | ||

*[http://www.st.com/web/catalog/mmc/FM141/SC1169/SS1577/LN1806/PF255419# STM32F429ZI resources] (click the Design Resources tab) | *[http://www.st.com/web/catalog/mmc/FM141/SC1169/SS1577/LN1806/PF255419# STM32F429ZI resources] (click the Design Resources tab) | ||

| − | |||

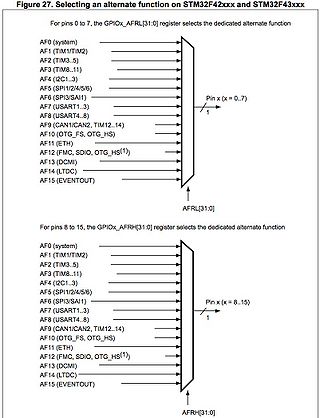

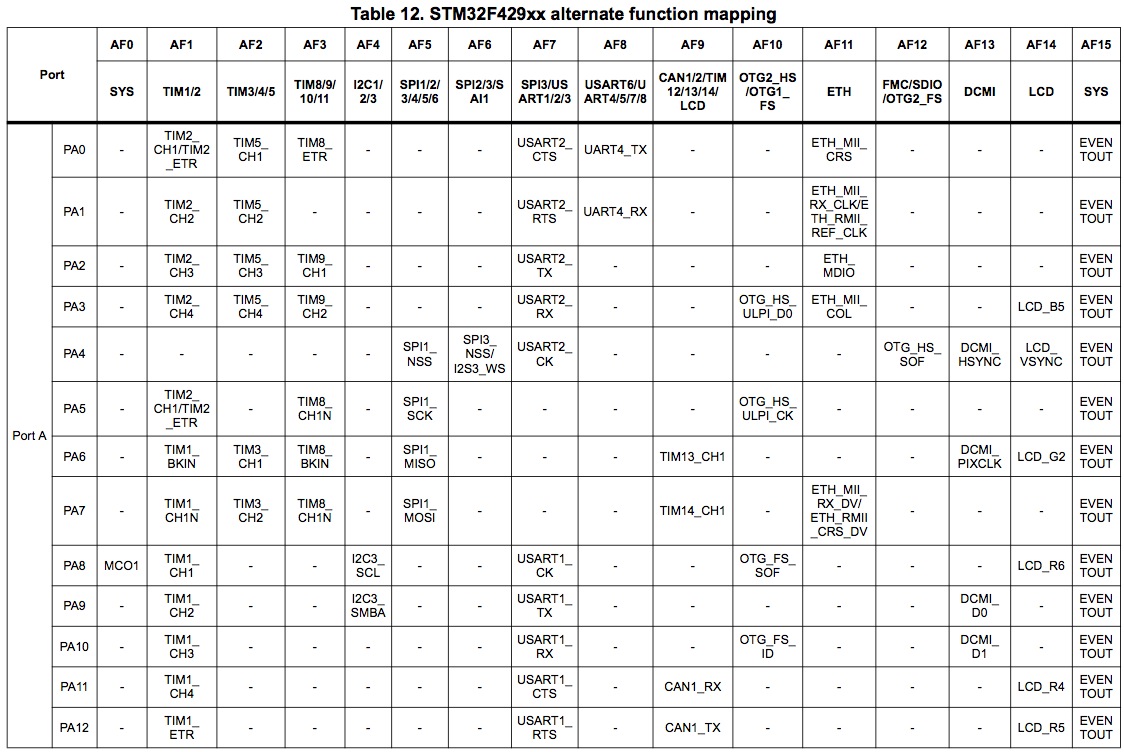

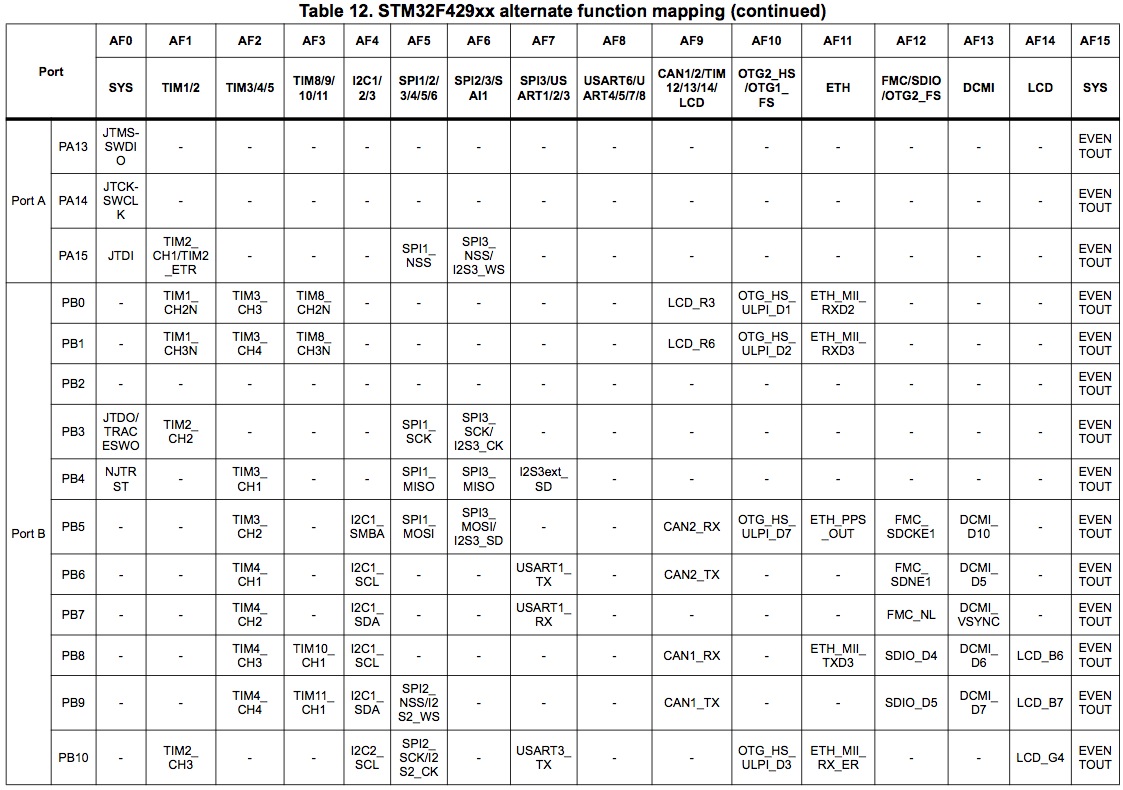

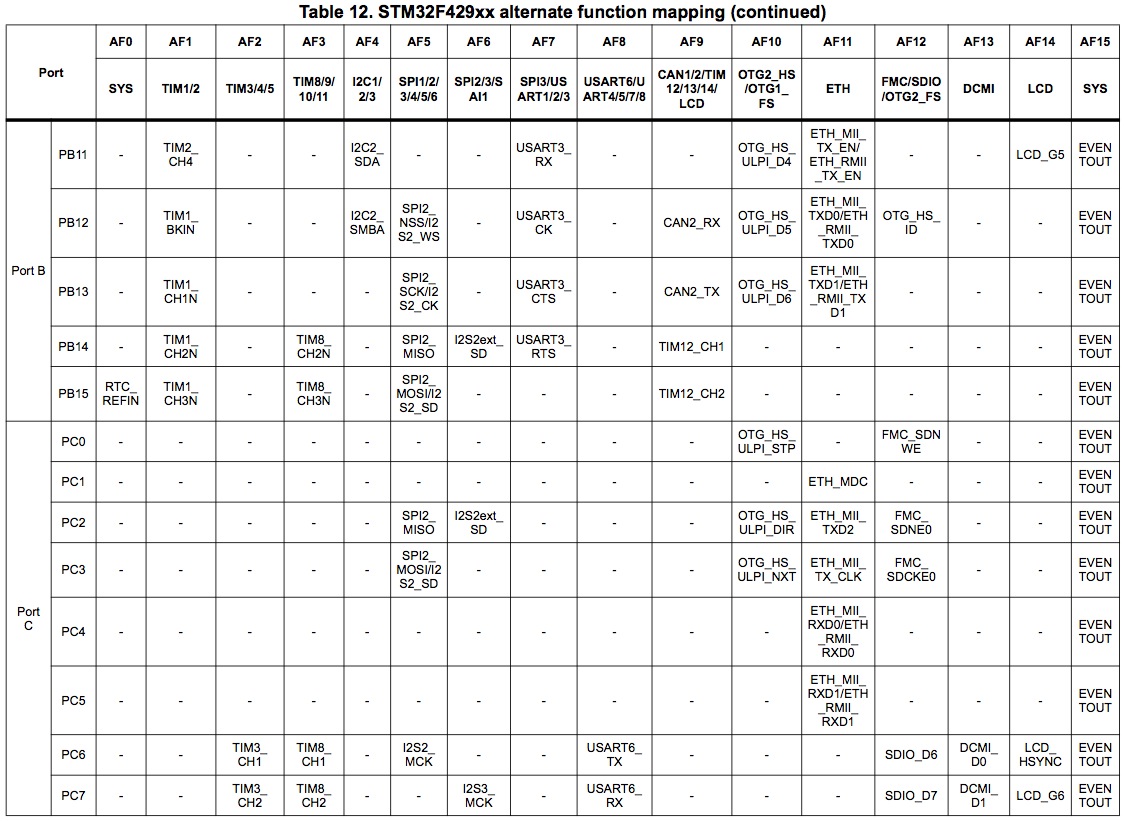

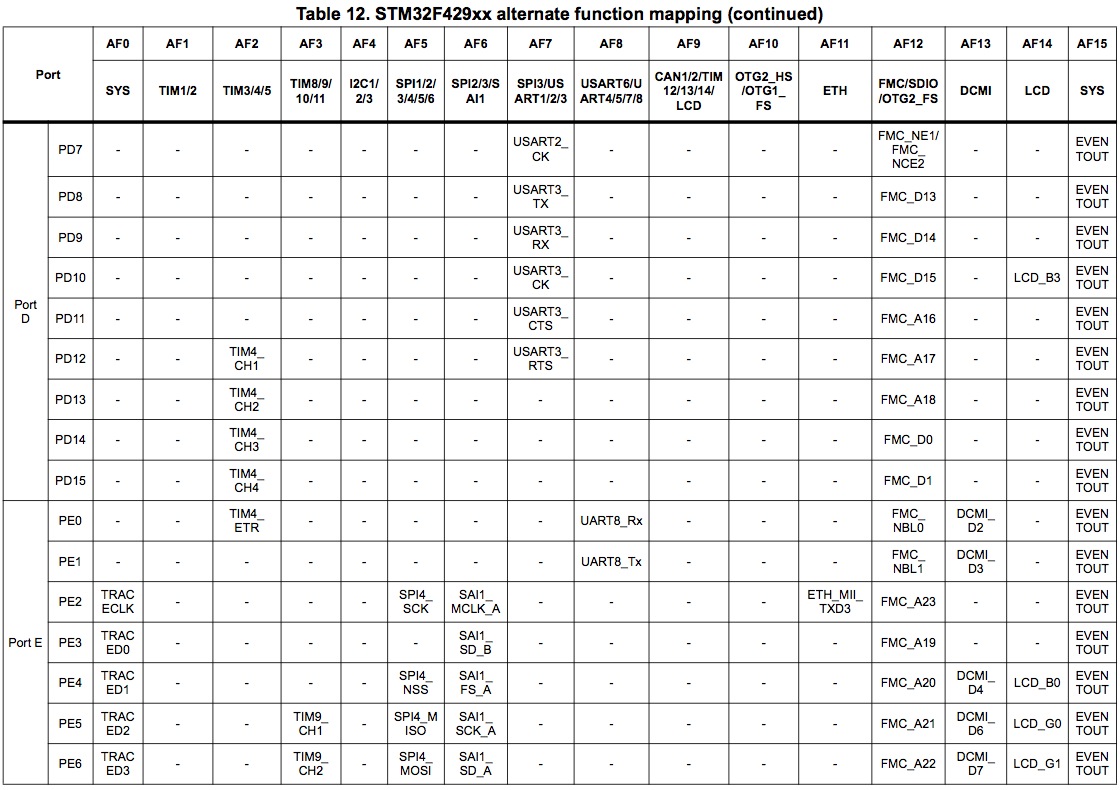

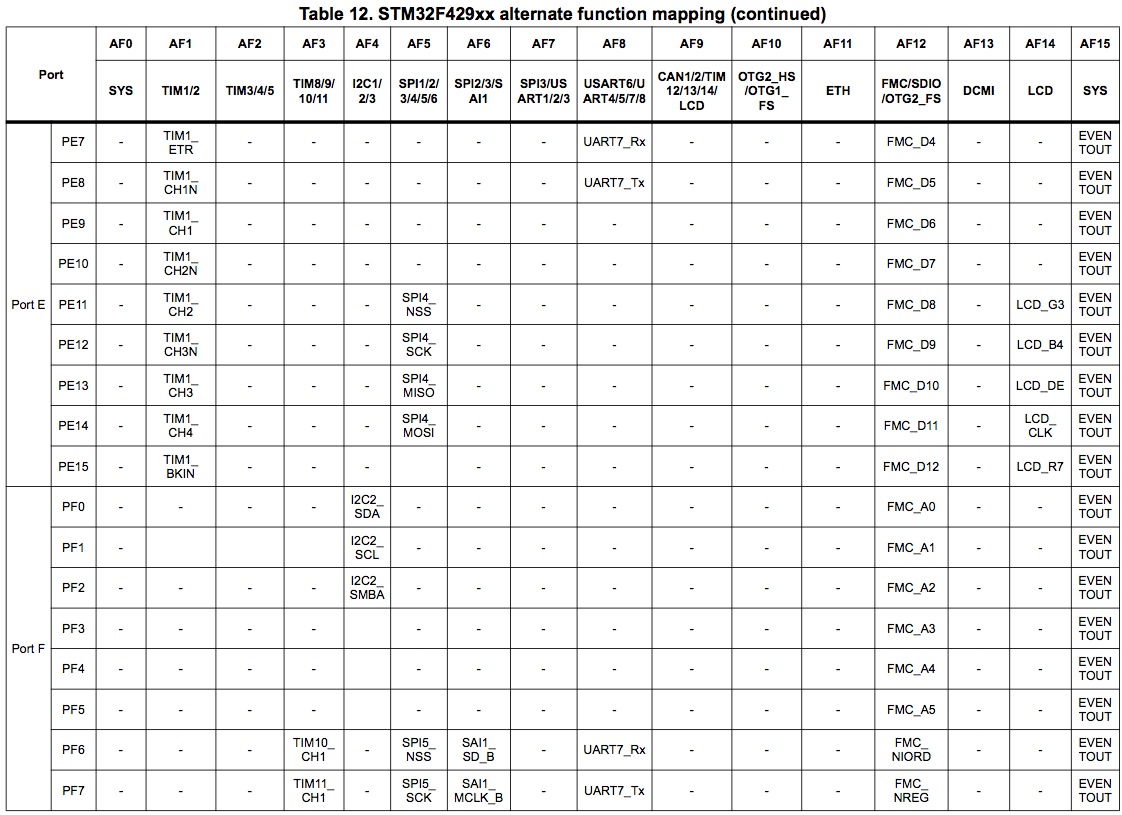

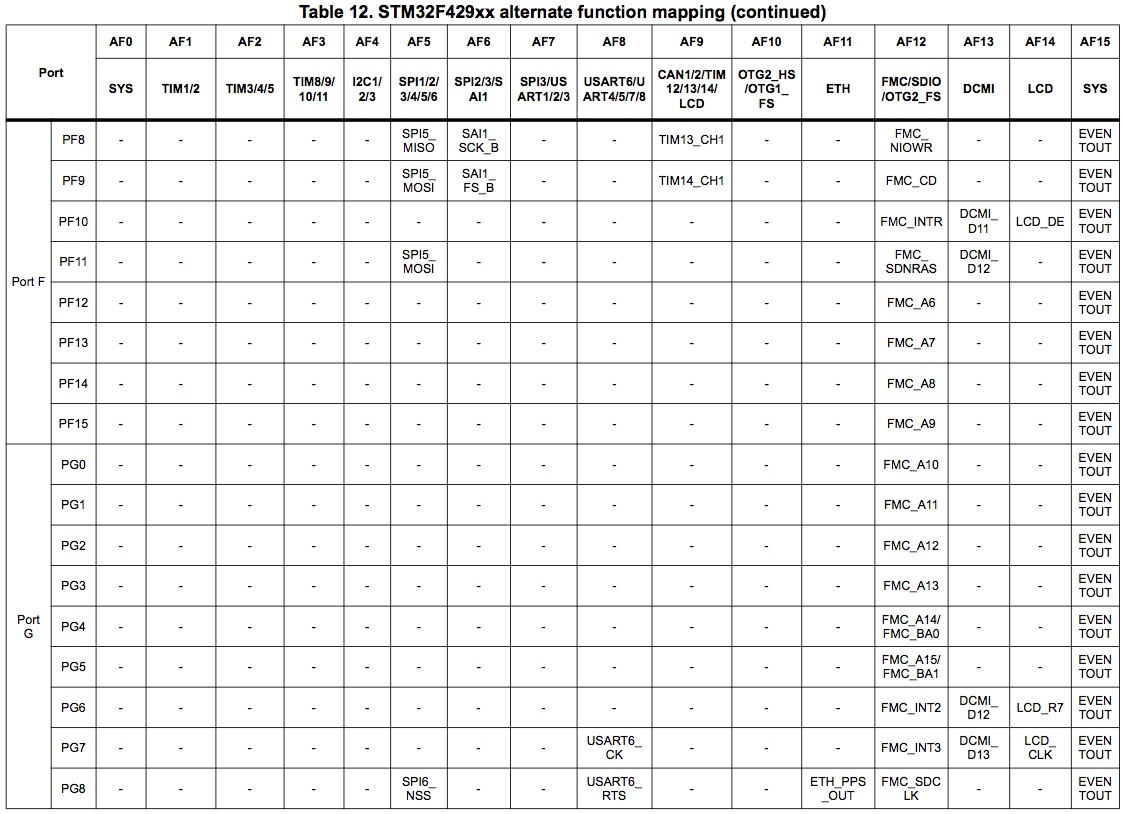

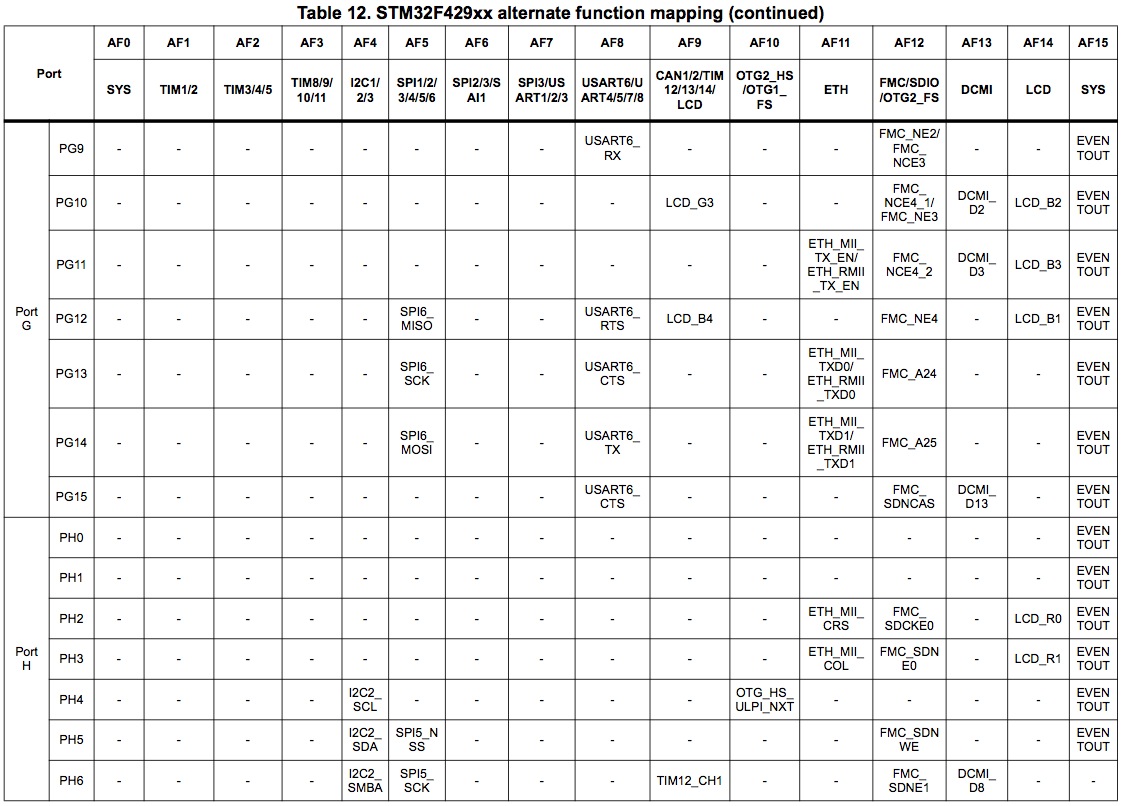

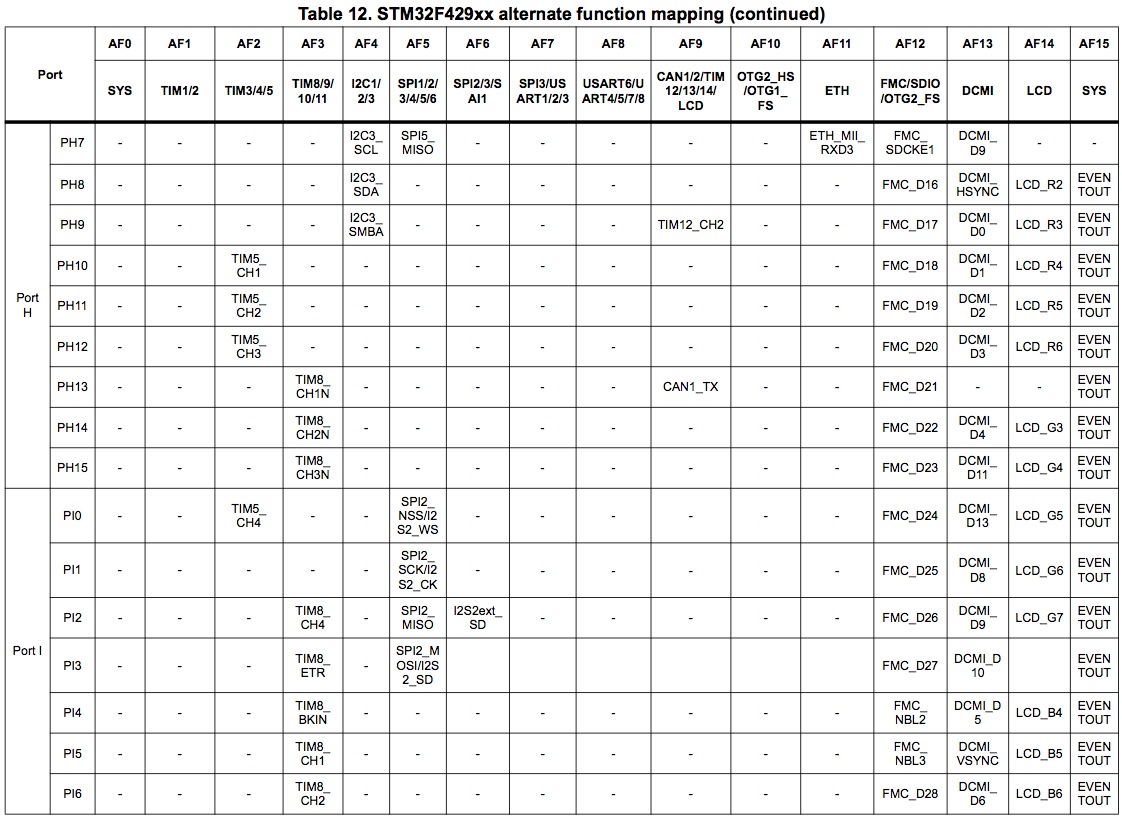

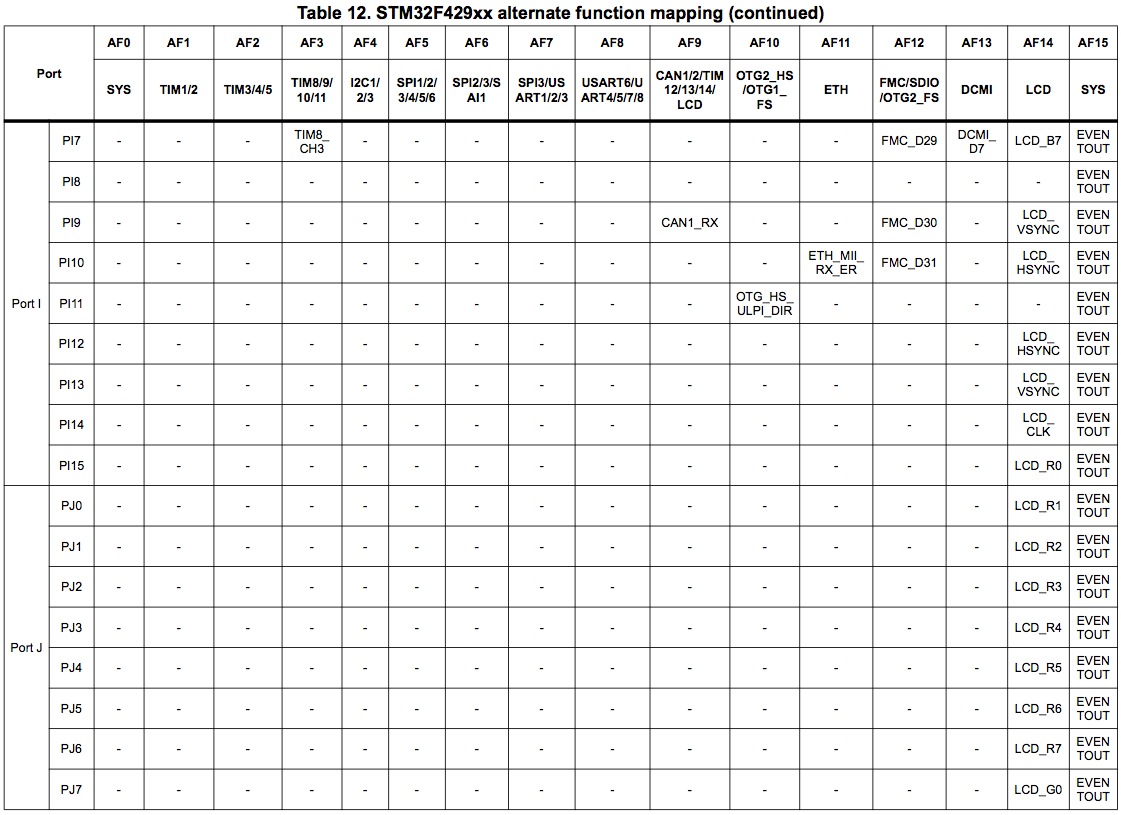

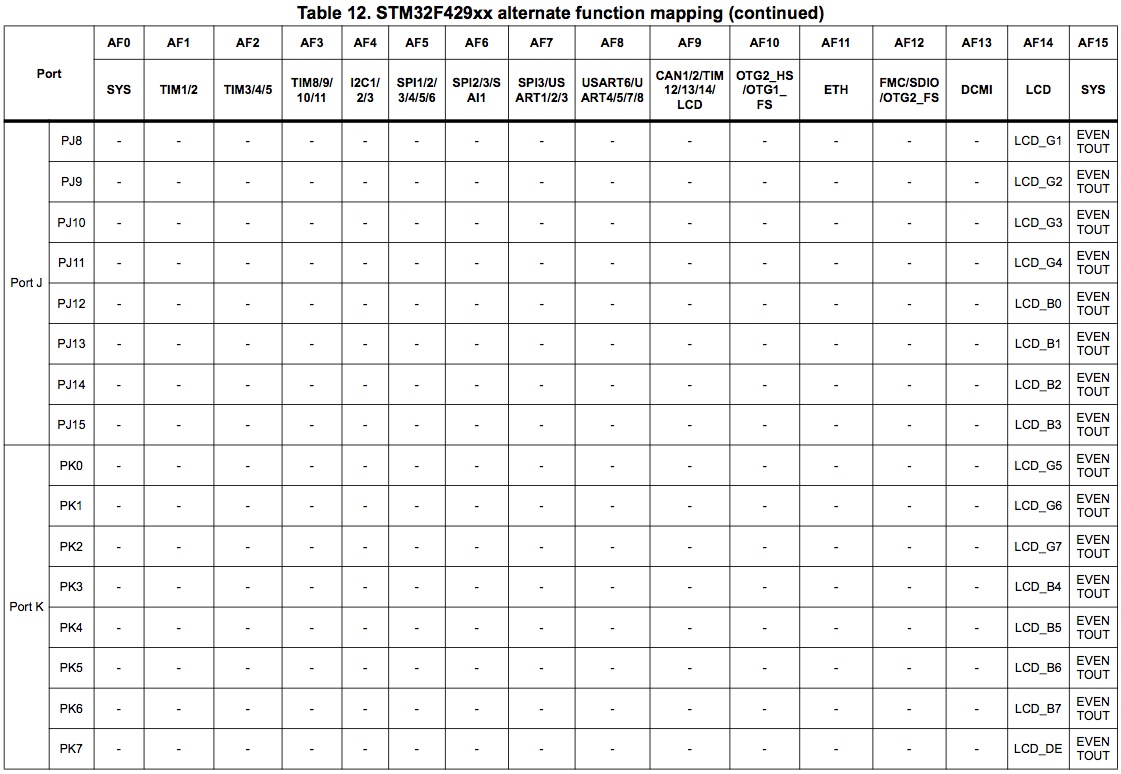

===Alternate function mapping=== | ===Alternate function mapping=== | ||

| Line 75: | Line 85: | ||

[[File:STM32F427_AF_mapping8.jpg]]<br /> | [[File:STM32F427_AF_mapping8.jpg]]<br /> | ||

[[File:STM32F427_AF_mapping9.jpg]]<br /> | [[File:STM32F427_AF_mapping9.jpg]]<br /> | ||

| + | |||

| + | |||

| + | ===External interrupt mapping=== | ||

| + | [[File:STM32F429_external_interrupts.JPG]] | ||

==[http://www.st.com/web/catalog/tools/FM116/SC959/SS1532/PF259090 32F429IDISCOVERY] Development Board Overview== | ==[http://www.st.com/web/catalog/tools/FM116/SC959/SS1532/PF259090 32F429IDISCOVERY] Development Board Overview== | ||

| Line 156: | Line 170: | ||

| '''11''' | | '''11''' | ||

| '''12''' | | '''12''' | ||

| − | | ''' | + | | '''13''' |

| '''14''' | | '''14''' | ||

| '''15''' | | '''15''' | ||

| Line 384: | Line 398: | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PA4 | | bgcolor="#FFFFFF" | PA4 | ||

| − | | bgcolor="#FFFFFF" align="center" | & | + | | bgcolor="#FFFFFF" align="center" | → |

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*LCD-TFT VSYNC | *LCD-TFT VSYNC | ||

*LCD-RGB VSYNC | *LCD-RGB VSYNC | ||

| − | |||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*SPI1_NSS | *SPI1_NSS | ||

| Line 400: | Line 413: | ||

*ADC12_IN4 | *ADC12_IN4 | ||

*DAC_OUT1 | *DAC_OUT1 | ||

| − | | bgcolor="#FFFFFF" | | + | | bgcolor="#FFFFFF" | |

| + | *Only 3.3V tolerant | ||

|- | |- | ||

| bgcolor="#FFFFFF" style="color:green" | PA5 | | bgcolor="#FFFFFF" style="color:green" | PA5 | ||

| bgcolor="#FFFFFF" align="center" | | | bgcolor="#FFFFFF" align="center" | | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| − | |||

| − | |||

| − | |||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

| + | *TIM2_CH1 | ||

| + | *TIM2_ETR | ||

| + | *TIM8_CH1N | ||

| + | *SPI1_SCK | ||

| + | *OTG_HS_ULPI_CK | ||

| + | *EVENTOUT | ||

| + | *ADC12_IN5 | ||

| + | *DAC_OUT2 | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *Only 3.3V tolerant | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PA6 | | bgcolor="#FFFFFF" | PA6 | ||

| Line 415: | Line 436: | ||

*LCD-TFT DB6 | *LCD-TFT DB6 | ||

*LCD-RGB G2 | *LCD-RGB G2 | ||

| − | |||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*TIM1_BKIN | *TIM1_BKIN | ||

| Line 432: | Line 452: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*ACP/RF RST | *ACP/RF RST | ||

| − | |||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*TIM1_CH1N | *TIM1_CH1N | ||

| Line 470: | Line 489: | ||

*DCMI_D0 | *DCMI_D0 | ||

*EVENTOUT | *EVENTOUT | ||

| − | * | + | *OTG_FS_VBUS |

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| Line 517: | Line 536: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*SWDIO | *SWDIO | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *JTMS-SWDIO | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PA14 | | bgcolor="#FFFFFF" | PA14 | ||

| Line 522: | Line 545: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*SWCLK | *SWCLK | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *JTCK-SWCLK | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PA15 | | bgcolor="#FFFFFF" | PA15 | ||

| Line 527: | Line 554: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*Touch panel INT | *Touch panel INT | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *JTDI | ||

| + | *TIM2_CH1 | ||

| + | *TIM2_ETR | ||

| + | *SPI1_NSS | ||

| + | *SPI3_NSS | ||

| + | *I2S3_WS | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#F0F0F0" style="color:darkgrey" | PB0 | | bgcolor="#F0F0F0" style="color:darkgrey" | PB0 | ||

| Line 572: | Line 608: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

*SWO | *SWO | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | *JTDO | ||

| + | *TRACESWO | ||

| + | *TIM2_CH2 | ||

| + | *SPI1_SCK | ||

| + | *SPI3_SCK | ||

| + | *I2S3_CK | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| bgcolor="#F0F0F0" style="color:green" | PB4 | | bgcolor="#F0F0F0" style="color:green" | PB4 | ||

| bgcolor="#F0F0F0" align="center" | | | bgcolor="#F0F0F0" align="center" | | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | |||

| + | | bgcolor="#F0F0F0" | | ||

| + | *NJTRST | ||

| + | *TIM3_CH1 | ||

| + | *SPI1_MISO | ||

| + | *SPI3_MISO | ||

| + | *I2S3EXT_SD | ||

| + | *EVENTOUT | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| Line 581: | Line 635: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

*SDRAM SDCKE1 | *SDRAM SDCKE1 | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | *TIM3_CH2 | ||

| + | *I2C1_SMBA | ||

| + | *SPI1_MOSI | ||

| + | *SPI3_MOSI | ||

| + | *I2S3_SD | ||

| + | *CAN2_RX | ||

| + | *OTG_HS_ULPI_D7 | ||

| + | *ETH_PPS_OUT | ||

| + | *FMC_SDCKE1 | ||

| + | *DCMI_D10 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PB6 | | bgcolor="#F0F0F0" | PB6 | ||

| Line 586: | Line 653: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

*SDRAM SDNE1 | *SDRAM SDNE1 | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | *TIM4_CH1 | ||

| + | *I2C1_SCL | ||

| + | *USART1_TX | ||

| + | *CAN2_TX | ||

| + | *FMC_SDNE1 | ||

| + | *DCMI_D5 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| bgcolor="#F0F0F0" style="color:green" | PB7 | | bgcolor="#F0F0F0" style="color:green" | PB7 | ||

| bgcolor="#F0F0F0" align="center" | | | bgcolor="#F0F0F0" align="center" | | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | |||

| + | | bgcolor="#F0F0F0" | | ||

| + | *TIM4_CH2 | ||

| + | *I2C1_SDA | ||

| + | *USART1_RX | ||

| + | *FMC_NL | ||

| + | *DCMI_VSYNC | ||

| + | *EVENTOUT | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| Line 596: | Line 681: | ||

*LCD-TFT DB4 | *LCD-TFT DB4 | ||

*LCD-RGB B6 | *LCD-RGB B6 | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | *TIM4_CH3 | ||

| + | *TIM10_CH1 | ||

| + | *I2C1_SCL | ||

| + | *CAN1_RX | ||

| + | *ETH_MII_TXD3 | ||

| + | *SDIO_D4 | ||

| + | *DCMI_D6 | ||

| + | *LCD_B6 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PB9 | | bgcolor="#F0F0F0" | PB9 | ||

| Line 602: | Line 698: | ||

*LCD-TFT DB5 | *LCD-TFT DB5 | ||

*LCD-RGB B7 | *LCD-RGB B7 | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | *TIM4_CH4 | ||

| + | *TIM11_CH1 | ||

| + | *I2C1_SDA | ||

| + | *SPI2_NSS | ||

| + | *I2S2_WS | ||

| + | *CAN1_TX | ||

| + | *SDIO_D5 | ||

| + | *DCMI_D7 | ||

| + | *LCD_B7 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PB10 | | bgcolor="#F0F0F0" | PB10 | ||

| Line 777: | Line 885: | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PC6 | | bgcolor="#FFFFFF" | PC6 | ||

| − | | bgcolor="#FFFFFF" align="center" | & | + | | bgcolor="#FFFFFF" align="center" | → |

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*LCD-TFT HSYNC | *LCD-TFT HSYNC | ||

| Line 842: | Line 950: | ||

*LCD-TFT DB12 | *LCD-TFT DB12 | ||

*LCD-RGB R2 | *LCD-RGB R2 | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *SPI3_SCK | ||

| + | *I2S3_CK | ||

| + | *USART3_TX | ||

| + | *UART4_TX | ||

| + | *SDIO_D2 | ||

| + | *DCMI_D8 | ||

| + | *LCD_R2 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#FFFFFF" style="color:green" | PC11 | | bgcolor="#FFFFFF" style="color:green" | PC11 | ||

| bgcolor="#FFFFFF" align="center" | | | bgcolor="#FFFFFF" align="center" | | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | |||

| + | | bgcolor="#FFFFFF" | | ||

| + | *I2S3ext_SD | ||

| + | *SPI3_MISO | ||

| + | *USART3_RX | ||

| + | *UART4_RX | ||

| + | *SDIO_D3 | ||

| + | *DCMI_D4 | ||

| + | *EVENTOUT | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#FFFFFF" style="color:green" | PC12 | | bgcolor="#FFFFFF" style="color:green" | PC12 | ||

| bgcolor="#FFFFFF" align="center" | | | bgcolor="#FFFFFF" align="center" | | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | |||

| + | | bgcolor="#FFFFFF" | | ||

| + | *SPI3_MOSI | ||

| + | *I2S3_SD | ||

| + | *USART3_CK | ||

| + | *UART5_TX | ||

| + | *SDIO_CK | ||

| + | *DCMI_D9 | ||

| + | *EVENTOUT | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| Line 887: | Line 1,025: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

*SDRAM D2 | *SDRAM D2 | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | *CAN1_RX | ||

| + | *FMC_D2 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| bgcolor="#F0F0F0" | PD1 | | bgcolor="#F0F0F0" | PD1 | ||

| Line 892: | Line 1,035: | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

*SDRAM D3 | *SDRAM D3 | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | *CAN1_TX | ||

| + | *FMC_D3 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| bgcolor="#F0F0F0" style="color:green" | PD2 | | bgcolor="#F0F0F0" style="color:green" | PD2 | ||

| bgcolor="#F0F0F0" align="center" | | | bgcolor="#F0F0F0" align="center" | | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | |||

| + | | bgcolor="#F0F0F0" | | ||

| + | *TIM3_ETR | ||

| + | *UART5_RX | ||

| + | *SDIO_CMD | ||

| + | *DCMI_D11 | ||

| + | *EVENTOUT | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| Line 902: | Line 1,058: | ||

*LCD-TFT DB11 | *LCD-TFT DB11 | ||

*LCD-RGB G7 | *LCD-RGB G7 | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | *SPI2_SCK | ||

| + | *I2S2_CK | ||

| + | *USART2_CTS | ||

| + | *FMC_CLK | ||

| + | *DCMI_D5 | ||

| + | *LCD_G7 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| bgcolor="#F0F0F0" style="color:green" | PD4 | | bgcolor="#F0F0F0" style="color:green" | PD4 | ||

| bgcolor="#F0F0F0" align="center" | | | bgcolor="#F0F0F0" align="center" | | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | |||

| + | | bgcolor="#F0F0F0" | | ||

| + | *USART2_RTS | ||

| + | *FMC_NOE | ||

| + | *EVENTOUT | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| bgcolor="#F0F0F0" style="color:green" | PD5 | | bgcolor="#F0F0F0" style="color:green" | PD5 | ||

| bgcolor="#F0F0F0" align="center" | | | bgcolor="#F0F0F0" align="center" | | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | |||

| + | | bgcolor="#F0F0F0" | | ||

| + | *USART2_TX | ||

| + | *FMC_NWE | ||

| + | *EVENTOUT | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| Line 916: | Line 1,093: | ||

*LCD-TFT DB0 | *LCD-TFT DB0 | ||

*LCD-RGB B2 | *LCD-RGB B2 | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | *SPI3_MOSI | ||

| + | *I2S3_SD | ||

| + | *SAI1_SD_A | ||

| + | *USART2_RX | ||

| + | *FMC_NWAIT | ||

| + | *DCMI_D10 | ||

| + | *LCD_B2 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| bgcolor="#F0F0F0" style="color:green" | PD7 | | bgcolor="#F0F0F0" style="color:green" | PD7 | ||

| bgcolor="#F0F0F0" align="center" | | | bgcolor="#F0F0F0" align="center" | | ||

| + | | bgcolor="#F0F0F0" | | ||

| + | |||

| + | | bgcolor="#F0F0F0" | | ||

| + | *USART2_CK | ||

| + | *FMC_NE1/FMC_NCE2 | ||

| + | *EVENTOUT | ||

| bgcolor="#F0F0F0" | | | bgcolor="#F0F0F0" | | ||

|- | |- | ||

| Line 1,008: | Line 1,201: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*SDRAM NBL0 | *SDRAM NBL0 | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *TIM4_ETR | ||

| + | *UART8_RX | ||

| + | *FMC_NBL0 | ||

| + | *DCMI_D2 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE1 | | bgcolor="#FFFFFF" | PE1 | ||

| Line 1,013: | Line 1,213: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*SDRAM NBL1 | *SDRAM NBL1 | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *UART8_TX | ||

| + | *FMC_NBL1 | ||

| + | *DCMI_D3 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#FFFFFF" style="color:green" | PE2 | | bgcolor="#FFFFFF" style="color:green" | PE2 | ||

| Line 1,081: | Line 1,287: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*SDRAM D4 | *SDRAM D4 | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *TIM1_ETR | ||

| + | *UART7_RX | ||

| + | *FMC_D4 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE8 | | bgcolor="#FFFFFF" | PE8 | ||

| Line 1,086: | Line 1,298: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*SDRAM D5 | *SDRAM D5 | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *TIM1_CH1N | ||

| + | *UART7_TX | ||

| + | *FMC_D5 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE9 | | bgcolor="#FFFFFF" | PE9 | ||

| Line 1,091: | Line 1,309: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*SDRAM D6 | *SDRAM D6 | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *TIM1_CH1 | ||

| + | *FMC_D6 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PE10 | | bgcolor="#FFFFFF" | PE10 | ||

| Line 1,430: | Line 1,653: | ||

| bgcolor="#FFFFFF" style="color:green" | PG9 | | bgcolor="#FFFFFF" style="color:green" | PG9 | ||

| bgcolor="#FFFFFF" align="center" | | | bgcolor="#FFFFFF" align="center" | | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | |||

| + | | bgcolor="#FFFFFF" | | ||

| + | *USART6_RX | ||

| + | *FMC_NE2 | ||

| + | *FMC_NCE3 | ||

| + | *EVENTOUT | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| Line 1,437: | Line 1,667: | ||

*LCD-TFT DB7 | *LCD-TFT DB7 | ||

*LCD-RGB G3 | *LCD-RGB G3 | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *LCD_G3 | ||

| + | *FMC_NCE4_1 | ||

| + | *FMC_NE3 | ||

| + | *DCMI_D2 | ||

| + | *LCD_B2 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG11 | | bgcolor="#FFFFFF" | PG11 | ||

| Line 1,443: | Line 1,681: | ||

*LCD-TFT DB1 | *LCD-TFT DB1 | ||

*LCD-RGB B3 | *LCD-RGB B3 | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *ETH_MII_TX_EN | ||

| + | *ETH_R_MII_TX_EN | ||

| + | *FMC_NCE4_2 | ||

| + | *DCMI_D3 | ||

| + | *LCD_B3 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG12 | | bgcolor="#FFFFFF" | PG12 | ||

| Line 1,449: | Line 1,695: | ||

*LCD-TFT DB2 | *LCD-TFT DB2 | ||

*LCD-RGB B4 | *LCD-RGB B4 | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *SPI6_MISO | ||

| + | *USART6_RTS | ||

| + | *LCD_B4 | ||

| + | *FMC_NE4 | ||

| + | *LCD_B1 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG13 | | bgcolor="#FFFFFF" | PG13 | ||

| Line 1,454: | Line 1,708: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*LED <span style="color:green">green</span> | *LED <span style="color:green">green</span> | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *SPI6_SCK | ||

| + | *USART6_CTS | ||

| + | *ETH_MII_TXD0 | ||

| + | *ETH_RMII_TXD0 | ||

| + | *FMC_A24 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG14 | | bgcolor="#FFFFFF" | PG14 | ||

| Line 1,459: | Line 1,721: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*LED <span style="color:red">red</span> | *LED <span style="color:red">red</span> | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *SPI6_MOSI | ||

| + | *USART6_TX | ||

| + | *ETH_MII_TXD1 | ||

| + | *ETH_RMII_TXD1 | ||

| + | *FMC_A25 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#FFFFFF" | PG15 | | bgcolor="#FFFFFF" | PG15 | ||

| Line 1,464: | Line 1,734: | ||

| bgcolor="#FFFFFF" | | | bgcolor="#FFFFFF" | | ||

*SDRAM SDNCAS | *SDRAM SDNCAS | ||

| + | | bgcolor="#FFFFFF" | | ||

| + | *USART6_CTS | ||

| + | *FMC_SDNCAS | ||

| + | *DCMI_D13 | ||

| + | *EVENTOUT | ||

| + | | bgcolor="#FFFFFF" | | ||

|- | |- | ||

| bgcolor="#F0F0F0" style="color:red" | PH0 | | bgcolor="#F0F0F0" style="color:red" | PH0 | ||

Latest revision as of 09:50, 29 October 2017

Contents

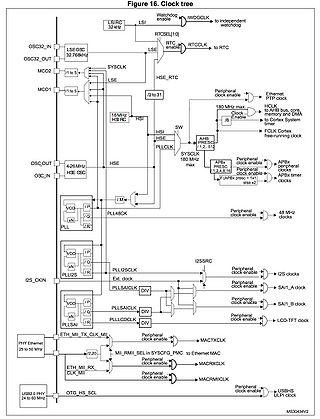

STM32F429ZIT6 Microcontroller Overview

- ARM Cortex-M4 32b MCU+FPU, 225DMIPS, up to 2MB Flash/256+4KB RAM, USB OTG HS/FS, Ethernet, 17 TIMs, 3 ADCs, 20 comm. interfaces, camera & LCD-TFT, Adaptive real-time accelerator (ART AcceleratorTM) allowing 0-wait state execution from Flash memory, frequency up to 180 MHz, and DSP instructions

- Memories

- Up to 2 MB of Flash memory organized into two banks allowing read-while-write

- Up to 256+4 KB of SRAM including 64-KB of CCM (core coupled memory) data RAM

- Flexible external memory controller with up to 32-bit data bus: SRAM,PSRAM,SDRAM, Compact Flash/NOR/NAND memories

- LCD parallel interface, 8080/6800 modes

- LCD-TFT controller up to VGA resolution with dedicated Chrom-ART AcceleratorTM for enhanced graphic content creation (DMA2D)

- Clock, reset and supply management

- 1.8 V to 3.6 V application supply and I/Os

- POR, PDR, PVD and BOR

- 4-to-26 MHz crystal oscillator

- Internal 16 MHz factory-trimmed RC (1% accuracy)

- 32 kHz oscillator for RTC with calibration

- Internal 32 kHz RC with calibration

- Low power

- Sleep, Stop and Standby modes

- VBAT supply for RTC, 20×32 bit backup registers + optional 4 KB backup SRAM

- 3×12-bit, 2.4 MSPS ADC: up to 24 channels and 7.2 MSPS in triple interleaved mode

- 2×12-bit D/A converters

- General-purpose DMA: 16-stream DMA controller with FIFOs and burst support

- Up to 17 timers: up to twelve 16-bit and two 32- bit timers up to 180 MHz, each with up to 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input

- Debug mode

- SWD & JTAG interfaces

- Cortex-M4 Embedded Trace MacrocellTM

- Up to 168 I/O ports with interrupt capability

- Up to 164 fast I/Os upto 84MHz

- Up to 166 5 V-tolerant I/Os

- Up to 21 communication interfaces

- Up to 3 × I2C interfaces (SMBus/PMBus)

- Up to 4 USARTs/4 UARTs (11.25 Mbit/s, ISO7816 interface, LIN, IrDA, modem control)

- Up to 6 SPIs (42 Mbits/s), 2 with muxed full-duplex I2S for audio class accuracy via internal audio PLL or external clock

- 1 x SAI (serial audio interface)

- 2 × CAN (2.0B Active) and SDIO interface

- Advanced connectivity

- USB 2.0 full-speed device/host/OTG controller with on-chip PHY

- USB 2.0 high-speed/full-speed device/host/OTG controller with dedicated DMA, on-chip full-speed PHY and ULPI

- 10/100 Ethernet MAC with dedicated DMA: supports IEEE 1588v2 hardware, MII/RMII

- 8 to 14-bit parallel camera interface up to 54 MBs/s

- True random number generator

- CRC calculation unit

- 96-bit unique ID

- RTC: subsecond accuracy, hardware calendar

Memory map

SRAM Name Address Size Bus Description SRAM1 0x2000 0000 112KB IDS Main internal SRAM SRAM2 0x2001 C000 16KB S Auxiliary internal SRAM SRAM3 0x2002 0000 64KB S Auxiliary internal SRAM CCM 0x1000 0000 64KB D Core coupled memory ( only accessible by CPU ) BKPSRAM 0x4002 4000 4KB S Backup SRAM ( Battery backup domain ) *I = Instruction bus, D = Data bus, S = System bus

Documents and files

- Latest version of Keil µVision (Register for free to get the download link)

- STM32F429ZI microcontroller datasheet

- ARM Cortex®-M4 Technical Reference Manual

- STM32F42xxx Reference Manual

- Programming manual

- STM32F429ZI resources (click the Design Resources tab)

Alternate function mapping

External interrupt mapping

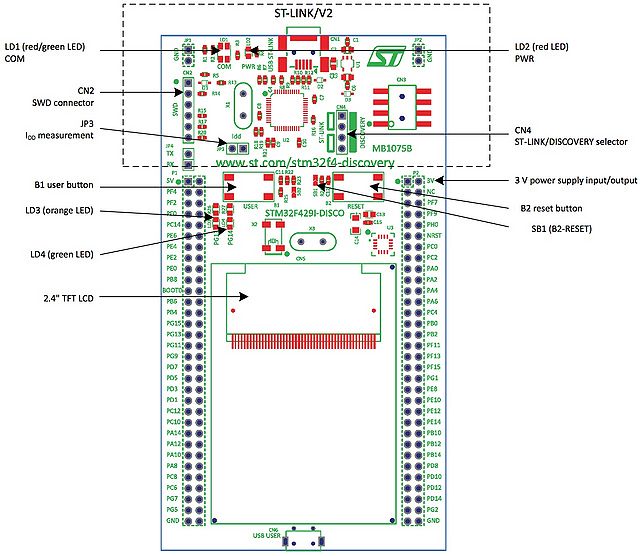

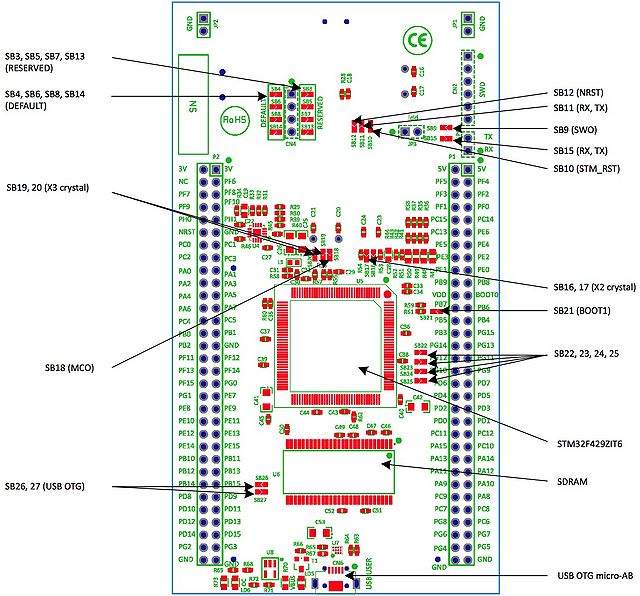

32F429IDISCOVERY Development Board Overview

- STM32F429ZIT6 microcontroller featuring

- 2 MB of Flash memory

- 256 KB of RAM

- LQFP144 package

- On-board ST-LINK/V2 with selection mode switch to use the kit as a standalone

- ST-LINK/V2 (with SWD connector for programming and debugging)

- Board power supply

- through the USB bus

- from an external 3 V or 5 V supply voltage

- 2.4" QVGA TFT LCD

- ILI9341 LCD controller

- SDRAM 64 Mbits

- L3GD20, ST MEMS motion sensor, 3-axis digital output gyroscope

- Six LEDs:

- LD1 (red/green) for USB communication

- LD2 (red) for 3.3 V power-on

- Two user LEDs

- LD3 (green) PG13

- LD4 (red) PG14

- Two USB OTG LEDs

- LD5 (green) VBUS

- LD6 (red) OC (over-current)

- Two pushbuttons

- user

- reset

- USB OTG with micro-AB connector

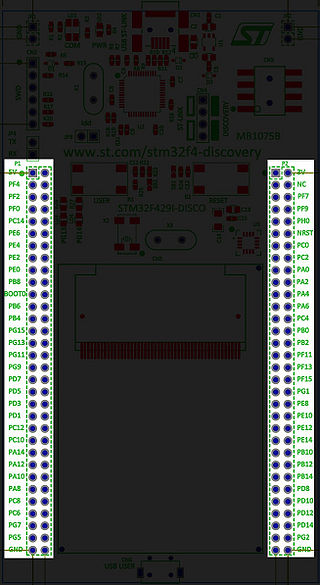

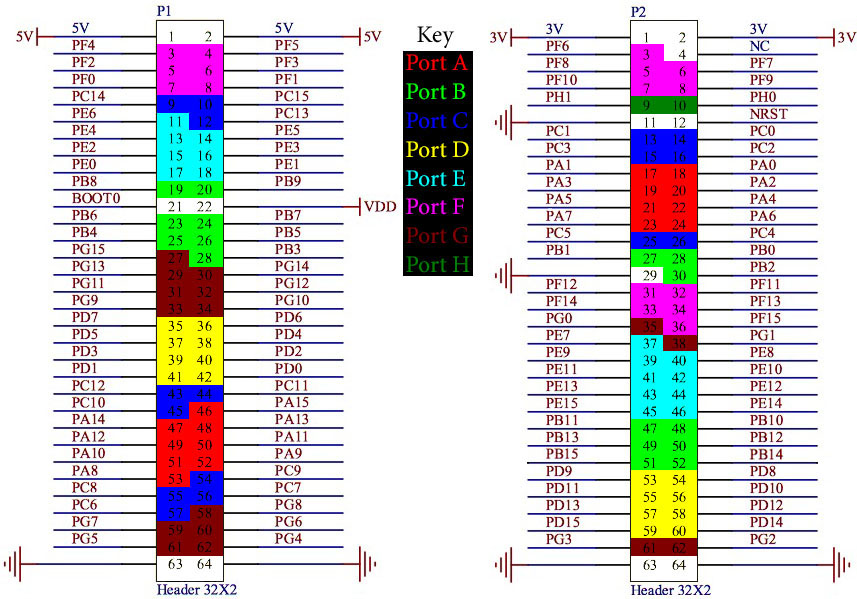

- Extension header for LQFP144 I/Os for a quick connection to the prototyping board and an easy probing

Documents and files

- Product Page 32F429IDISCOVERYDiscovery kit for STM32 F429/439 lines - with STM32F429ZI MCU

- Discovery kit for STM32F429/439 lines board data brief

- Schematic

- User Manual Discovery kit for STM32F429/439 lines (board overview, diagrams and schematics, used pins)

- Getting started with the STM32F429 Discovery kit (connecting and programming)

- Getting started with STM32F429 Discovery software development tools (programming and IDEs)

- STSW-STM32138STM32F429 discovery firmware package (UM1662)

- STM32F429 discovery .Net Micro Framework package (UM1676)

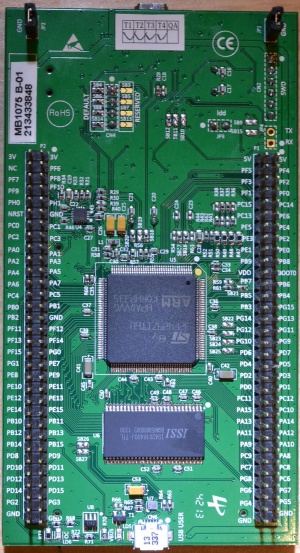

Board Layout

| Front View |

|

| Back View |

|

Pinout

Available pins on board

| Bit | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| Port A | PA0 | PA1 | PA2 | PA3 | PA4 | PA5 | PA6 | PA7 | PA8 | PA9 | PA10 | PA11 | PA12 | PA13 | PA14 | PA15 |

| Port B | PB3 | PB4 | PB5 | PB6 | PB7 | PB8 | PB9 | PB10 | PB11 | PB12 | PB13 | PB14 | PB15 | |||

| Port C | PC0 | PC1 | PC2 | PC3 | PC4 | PC5 | PC6 | PC7 | PC8 | PC9 | PC10 | PC11 | PC12 | PC13 | PC14 | PC15 |

| Port D | PD0 | PD1 | PD2 | PD3 | PD4 | PD5 | PD6 | PD7 | PD8 | PD9 | PD10 | PD11 | PD12 | PD13 | PD14 | PD15 |

| Port E | PE0 | PE1 | PE2 | PE3 | PE4 | PE5 | PE6 | PE7 | PE8 | PE9 | PE10 | PE11 | PE12 | PE13 | PE14 | PE15 |

| Port F | PF0 | PF1 | PF2 | PF3 | PF4 | PF5 | PF6 | PF11 | PF12 | PF13 | PF14 | PF15 | ||||

| Port G | PG0 | PG1 | PG2 | PG3 | PG4 | PG5 | PG6 | PG7 | PG8 | PG9 | PG10 | PG11 | PG12 | PG13 | PG14 | PG15 |

| Port H | PH0 | PH1 |

PCB IO map

Key

Pin not used. Fully available

Pin used. May be available if peripheral is not used, peripheral input pin, or led pin

Pin used. Do not use this pin.

Pin not broken out

| Pin | Direction | Connected to | Alternate functions | Notes |

| PA0 | ← |

|

|

|

| PA1 | ← |

|

|

|

| PA2 | ← |

|

|

|

| PA3 | ↔ |

|

|

|

| PA4 | → |

|

|

|

| PA5 |

|

| ||

| PA6 | ↔ |

|

|

|

| PA7 | ? |

|

|

|

| PA8 | ? |

|

|

|

| PA9 |

|

|||

| PA10 |

|

|||

| PA11 | ↔ |

|

|

|

| PA12 | ↔ |

|

|

|

| PA13 | ? |

|

|

|

| PA14 | ? |

|

|

|

| PA15 | ← |

|

|

|

| PB0 | ↔ |

|

|

|

| PB1 | ↔ |

|

|

|

| PB2 | ? |

|

|

|

| PB3 | ? |

|

|

|

| PB4 |

|

|||

| PB5 | ? |

|

|

|

| PB6 | ? |

|

|

|

| PB7 |

|

|||

| PB8 | ↔ |

|

|

|

| PB9 | ↔ |

|

|

|

| PB10 | ↔ |

|

|

|

| PB11 | ↔ |

|

|

|

| PB12 | ? |

|

|

|

| PB13 | ← ? |

|

|

|

| PB14 | ↔ |

|

|

|

| PB15 | ↔ |

|

|

|

| PC0 | ? |

|

|

|

| PC1 | → |

|

|

|

| PC2 | ? |

|

|

|

| PC3 |

|

|||

| PC4 | ? |

|

|

|

| PC5 | ? |

|

|

|

| PC6 | → |

|

|

|

| PC7 | ↔ |

|

|

|

| PC8 |

|

|||

| PC9 | ? |

|

|

|

| PC10 | ↔ |

|

|

|

| PC11 |

|

|||

| PC12 |

|

|||

| PC13 |

|

| ||

| PC14 |

|

|

| |

| PC15 |

|

|

| |

| PD0 | ↔ |

|

|

|

| PD1 | ↔ |

|

|

|

| PD2 |

|

|||

| PD3 | ↔ |

|

|

|

| PD4 |

|

|||

| PD5 |

|

|||

| PD6 | ↔ |

|

|

|

| PD7 |

|

|||

| PD8 | ↔ |

|

|

|

| PD9 | ↔ |

|

|

|

| PD10 | ↔ |

|

|

|

| PD11 | → ? |

|

|

|

| PD12 | → ? |

|

|

|

| PD13 | → ? |

|

|

|

| PD14 | ↔ |

|

|

|

| PD15 | ↔ |

|

|

|

| PE0 | ? |

|

|

|

| PE1 | ? |

|

|

|

| PE2 |

|

|||

| PE3 |

|

|||

| PE4 |

|

|||

| PE5 |

|

|||

| PE6 |

|

|||

| PE7 | ↔ |

|

|

|

| PE8 | ↔ |

|

|

|

| PE9 | ↔ |

|

|

|

| PE10 | ↔ |

|

|

|

| PE11 | ↔ |

|

|

|

| PE12 | ↔ |

|

|

|

| PE13 | ↔ |

|

|

|

| PE14 | ↔ |

|

|

|

| PE15 | ↔ |

|

|

|

| PF0 | → |

|

|

|

| PF1 | → |

|

|

|

| PF2 | → |

|

|

|

| PF3 | → |

|

|

|

| PF4 | → |

|

|

|

| PF5 | → |

|

|

|

| PF6 |

|

|||

| PF7 | ? |

|

|

|

| PF8 | ← |

|

|

|

| PF9 | ? |

|

|

|

| PF10 | → |

|

|

|

| PF11 | ? |

|

|

|

| PF12 | → |

|

|

|

| PF13 | → |

|

|

|

| PF14 | → |

|

|

|

| PF15 | → |

|

|

|

| PG0 | → |

|

|

|

| PG1 | → |

|

|

|

| PG2 |

|

|||

| PG3 |

|

|||

| PG4 | ? |

|

|

|

| PG5 | ? |

|

|

|

| PG6 | ↔ |

|

|

|

| PG7 | ? |

|

|

|

| PG8 | → |

|

|

|

| PG9 |

|

|||

| PG10 | ↔ |

|

|

|

| PG11 | ↔ |

|

|

|

| PG12 | ↔ |

|

|

|

| PG13 | → |

|

|

|

| PG14 | → |

|

|

|

| PG15 | ? |

|

|

|

| PH0 | ← |

|

|

|

| PH1 | → |

|

|

|

| PH2 | ||||

| PH3 | ||||

| PH4 | ||||

| PH5 | ||||

| PH6 | ||||

| PH7 | ||||

| PH8 | ||||

| PH9 | ||||

| PH10 | ||||

| PH11 | ||||

| PH12 | ||||

| PH13 | ||||

| PH14 | ||||

| PH15 | ||||

| PI0 | ||||

| PI1 | ||||

| PI2 | ||||

| PI3 | ||||

| PI4 | ||||

| PI5 | ||||

| PI6 | ||||

| PI7 | ||||

| PI8 | ||||

| PI9 | ||||

| PI10 | ||||

| PI11 | ||||

| PI12 | ||||

| PI13 | ||||

| PI14 | ||||

| PI15 | ||||

| PJ0 | ||||

| PJ1 | ||||

| PJ2 | ||||

| PJ3 | ||||

| PJ4 | ||||

| PJ5 | ||||

| PJ6 | ||||

| PJ7 | ||||

| PJ8 | ||||

| PJ9 | ||||

| PJ10 | ||||

| PJ11 | ||||

| PJ12 | ||||

| PJ13 | ||||

| PJ14 | ||||

| PJ15 | ||||

| PK0 | ||||

| PK1 | ||||

| PK2 | ||||

| PK3 | ||||

| PK4 | ||||

| PK5 | ||||

| PK6 | ||||

| PK7 |